Tổng số phụ: 45.360 VNĐ (gồm VAT)

Tổng quan kiến trúc ARM Cortex-M3 Để lại bình luận

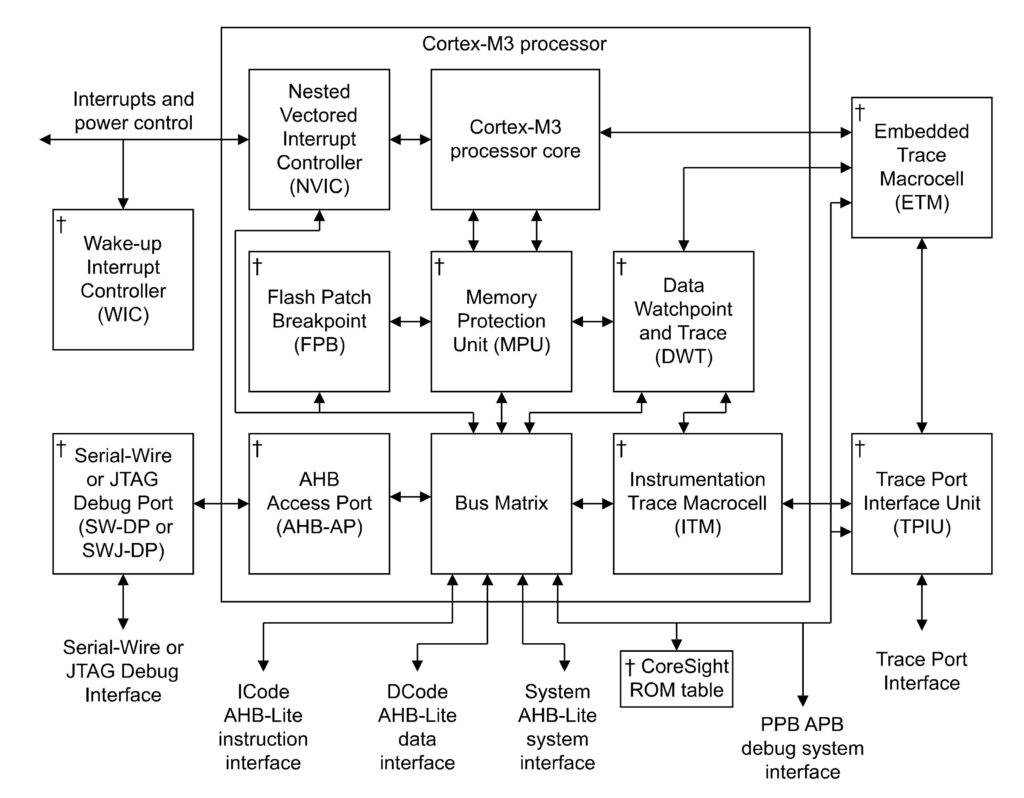

Arm Cortex-M3 là một bộ xử lý tiết kiệm năng lượng với thiết kế đơn giản, các tác vụ ngắt có độ trễ thấp, và bộ debug có chi phí thấp. Được thiết kế cho các ứng dụng nhúng chuyên sâu, nơi cần tính năng phản hồi ngắt nhanh FIQ (Fast Interrupt Request). Vậy điều gì đã làm nên những ưu điểm vượt trội của kiến trúc ARM Cortex-M3? Hãy cùng chipstack.vn tìm hiểu sâu hơn qua bài viết dưới đây nhé!

Xem thêm: Hệ thống nhúng là gì?

Một số tính năng chính:

Bộ xử lý Cortex-M3 tích hợp:

- Một CPU Cortex-M3.

- Nested Vectored Interrupt Controller (NVIC) được tích hợp gần với CPU để mang lại độ trễ thấp nhất có thể, đáp ứng nhu cầu của các tác vụ ngắt.

- Nhiều giao diện bus hiệu suất cao.

- Bộ debug chi phí thấp: breakpoints, watchpoints, tracing, Trace Port Analyzer…

- Memory Protection Unit (MPU).

Kiến trúc ARM Cortex-M3

Cortex-M3 processor core

Được xây dựng dựa trên kiến trúc ARMv7-M, Cortex-M3 processor core thực thi các câu lệnh, phép toán.

Kiến trúc ARMv7-M sử dụng Thumb-2 instruction set là sự kết hợp giữa Thumb (16-bit) và ARM32 (32-bit). Mục đích để giảm được kích thước của mỗi câu lệnh xuống 16-bit do đó tiết kiệm không gian lưu trữ của Thumb trong khi vẫn hoạt động được với các thanh ghi địa chỉ 32-bit và giữ được hiệu suất nhanh giống ARM32. Do đó, Thumb-2 vừa tiết kiệm không gian lưu trữ, hiệu năng và có hiệu suất cao.

Nested Vectored Interrupt Controller:

Mục đích của NVIC là:

- Để xử lý các tín hiệu ngắt (Handles interrupts) theo thứ tự ưu tiên dựa vào Interrupt Vector Table.

- Cấu hình preemption priority.

Khi một tín hiệu ngắt xảy ra, NVIC sẽ xác định tín hiệu ngắt có độ ưu tiên cao nhất, truy xuất địa chỉ của tín hiệu ngắt này sau đó gửi đến cho Cortex-M3 processor core xử lý tín hiệu này.

NVIC hỗ trợ lên đến 240 tác vụ ngắt với 256 mức độ ưu tiên khác nhau.

NVIC cho phép các khả năng để có thể cấu hình được các tác vụ ngắt với độ trễ thấp vì được tích hợp gần với Cortex-M3 processor core và cấu hình được hiệu năng sử dụng Wake-up Interrupt Controller.

Wake-up Interrupt Controller (WIC)

WIC là một ngoại vi phát hiện tín hiệu ngắt để “đánh thức” processor từ chế độ deep sleep trong kiến trúc ARM Cortex-M3. WIC chỉ hoạt động khi hệ thống đang được bật ở chế độ deep sleep.

Khi WIC được bật và processor ở chế độ deep sleep, bộ Power Control đưa processor vào chế độ deep sleep. Khi WIC nhận được tín hiệu ngắt, phải mất một vài xung clock để “đánh thức” processor để có thể xử lý tín hiệu ngắt này, điều này làm cho độ trễ tăng lên khi trong chế độ deep sleep.

WIC không có thanh ghi và cũng không thể cấu hình lập trình theo người dùng được. Hoạt động dựa vào hoàn toàn tín hiệu từ phần cứng.

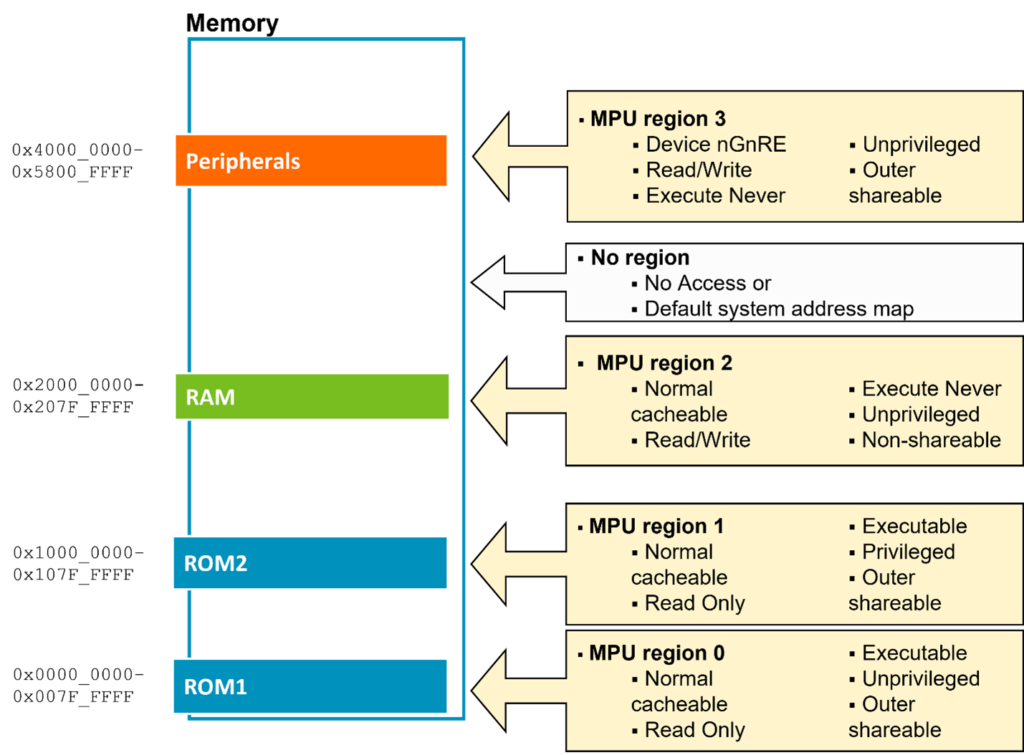

Memory Protection Unit (MPU)

Vai trò của MPU trong kiến trúc ARM Cortex-M3:

- Trong các hệ thống yêu cầu độ tin cậy cao (như thiết bị y tế), MPU giúp bảo vệ các vùng nhớ bằng cách thiết lập quyền truy cập. Ví dụ: chỉ cho phép một số phần mềm cụ thể đọc hoặc ghi dữ liệu vào vùng nhớ đó, do đó giúp bảo vệ quyền riêng tư dữ liệu ở cấp độ phần cứng.

- MPU cũng được định nghĩa là thuộc tính bộ nhớ, như là khả năng lưu trữ tạm (Cacheability), khi đó dữ liệu được Cacheability sẽ được gửi đến bộ nhớ đệm (cache) hoặc bộ điều khiển bộ nhớ (memory controller) để tối ưu hoá hiệu suất.

MPU cho phép phần mềm đặc quyền định nghĩa các vùng nhớ và thiết lập:

- Quyền truy cập (chỉ đọc, đọc – ghi)

- Thuộc tính bộ nhớ (có lưu trữ tạm – cacheable, hoặc chia sẻ được – sharable)

Sau khi vùng nhớ đó được thiết lập theo các thuộc tính trên, và khi CPU thực hiện một thao tác như (đọc, ghi, hoặc lấy lệnh), MPU sẽ:

- So địa chỉ truy cập có khớp với địa chỉ vùng nhớ đã được định nghĩa bởi MPU không.

- Nếu khớp địa chỉ thì kiểm tra xem thao tác truy cập có tuân thủ các quyền truy cập hay thuộc tính bộ nhớ không.

- Nếu phát hiện một vi phạm truy cập, MPU sẽ chặn thao tác truy cập, kích hoạt lỗi ngoại lệ bộ nhớ (MemManage Fault) để báo cho hệ thống.

Data Watchpoint and Trace (DWT)

DWT là đơn vị theo dõi và truy vết dữ liệu của Processor, nói một cách dễ hiểu DWT phục vụ cho mục đích gỡ lỗi (debugging) khi có một sự kiện nào đó xảy ra trong kiến trúc ARM Cortex-M3:

Ví dụ: Bạn muốn giám sát dữ liệu của một biến sensorData, và bạn muốn dữ liệu này nằm trong khoảng từ 0-100 nhưng kết quả lại ra 200. Khi đó: bạn cần cấu hình DWT comparator để giám sát địa chỉ bộ nhớ của sensorData, khi có bất kỳ lệnh nào ghi (write) vào biến sensorData thì một watchpoint event được kích hoạt và đưa CPU vào chế độ debug, Tạm dừng chương trình tại vị trí ghi đè đó giúp bạn xem điều gì đã ghi vào biến sensorData.

DWT cung cấp một số chức năng như:

- So sánh (Comparators):

- Theo dõi các địa chỉ dữ liệu.

- Kích hoạt các sự kiện:

- Watchpoint: CPU chuyển sang trạng thái debug.

- Data trace packets: Ghi lại các thông tin truy cập dữ liệu.

- Truy vết dữ liệu (Data tracing): Ghi lại địa chỉ, giá trị dữ liệu khi có sự kiện khớp.

- Truy vết thanh ghi chương trình (PC tracing): Ghi lại giá trị PC (Program counter) khi xảy ra sự kiện cụ thể.

- Thống kê hiệu suất (Performance profiling): Đếm chu kỳ và theo dõi các sự kiện liên quan đến hiệu suất.

Flash Patch Breakpoint (FPB)

FPB cung cấp khả năng đặt breakpoint và chỉnh sửa mã trực tiếp trong bộ nhớ flash mà không cần thay đổi đoạn mã gốc. FPB sử dụng bộ comparator để kiểm tra các địa chỉ quyết định xem liệu chương trình có dừng lại ở đó hay không.

Nếu MPU được bật, thì MPU sẽ kiểm tra xem vùng này có vi phạm các quy tắc đã được cấu hình từ trước hay không, nếu không thì địa chỉ gốc mới được remap đến lệnh breakpoint.

Instrumentation Trace Macrocell (ITM)

ITM là kiểu debug tương tự như lệnh printf.

Giúp bạn theo dõi được dữ liệu hệ thống trong quá trình debug.

ITM xuất thông tin dưới dạng các gói dữ liệu (packets), các gói dữ liệu có thể từ nhiều nguồn:

- Software trace: Phần mềm ghi trực tiếp vào các thanh ghi (stimulus registers) của ITM để tạo ra các gói dữ liệu.

- Hardware trace: DWT như đã nhắc ở trên sẽ tạo ra các gói dữ liệu để ITM xuất thông tin chúng ra.

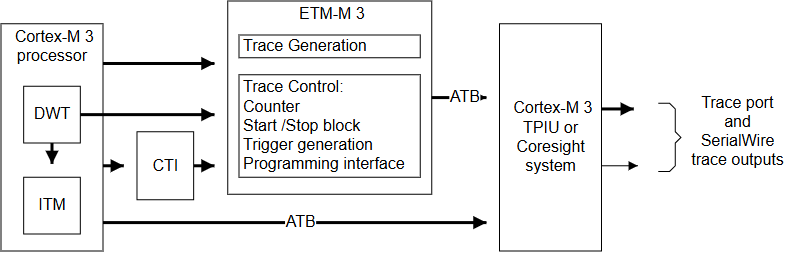

Embedded Trace Macrocell (ETM)

ETM là thành phần tuỳ chọn để hỗ trợ debug, giúp theo dõi chương trình đã chạy như thế nào trên vi điều khiển. Nó giống như một chiếc máy quay, ghi lại các lệnh mà CPU đã thực thi, từ đó kiểm tra xem chương trình đã chạy đúng như mình mong muốn hay chưa.

ETM nhận dữ liệu từ ghi lại các lệnh thực thi từ CPU và tạo ra các dữ liệu trace: counter (thời gian, sự kiện), Start/stop (Điều khiển bắt đầu/kết thúc trace), Trigger Generation (Kích hoạt tín hiệu trace dựa trên các sự kiện).

ETM sau đó xuất dữ liệu trace thông qua ATP.

TÓM TẮT DÒNG CHẢY DỮ LIỆU TỪ DWT/ITM SANG ETM:

- CPU thực thi lệnh, phát sinh các sự kiện, DWT và ITM ghi lại dữ liệu.

- Dữ liệu được truyền qua cho ETM để tạo ra các trace.

- ETM được xuất qua TPIU hoặc CoreSight để gửi đến công cụ debug bên ngoài.

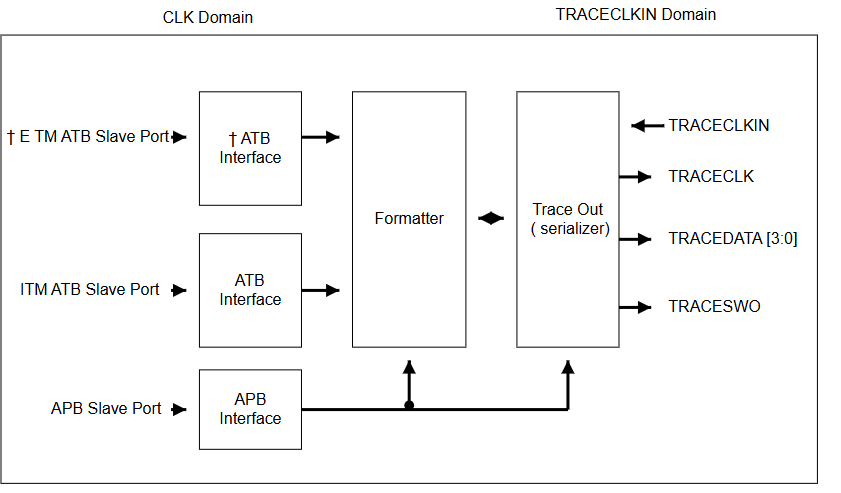

Trace Port Interface Unit (TPIU)

TPIU xuất dữ liệu trace ra ngoài qua các cổng Trace Port hoặc qua giao thức Serial Wire Viewer.

Khi dữ liệu trace được xuất sang TPIU thì cần phải định dạng dữ liệu (Formatter) – ghép các nguồn dữ liệu thành một dòng duy nhất, dữ liệu được đóng gói theo một chuẩn duy nhất, sau đó được xuất sang TRACEOUT.

TRACECLKIN: Nhận tín hiệu clock đầu vào để điều khiển việc xuất dữ liệu trace.

TRACECLK: Phát tín hiệu clock đồng bộ với dữ liệu trace.

Sau đó ta có thể chọn 1 trong 2 cách xuất nối tiếp hoặc song song:

TRACEDATA [3:0]: Xuất dữ liệu trace đã được định dạng dưới dạng song song qua cổng này (4 bit mỗi chu kỳ).

TRACESWO: Xuất dữ liệu trace dưới dạng nối tiếp (serial) cho giao thức Serial Wire Viewer (SWV)

AHB-Access port

AHB-AP (Advanced High-performance Bus – Access Port) là một cổng truy cập bộ nhớ (Memory Access Port – MEM-AP).

Đây là một cổng debug cho phép truy cập toàn bộ bộ nhớ và thanh ghi của hệ thống, truy cập thanh ghi vi xử lý thông qua System Control Space (SCS).

SW-DP (Serial Wire Debug Port) hoặc SWJ-DP (Serial Wire/JTAG Debug Port) được sử dụng để kết nối và gửi lệnh điều khiển đến AHB-AP.

- SW-DP: Giao thức debug nối tiếp.

- SWJ-DP: Giao thức hỗn hợp hỗ trợ cả nối tiếp (Serial Wire) và JTAG.

Ví dụ cách thức debug:

- Sử dụng công cụ debug (ví dụ: Keil hoặc OpenOCD) sử dụng SW-DP/SWJ-DP để gửi lệnh đến AHB-AP.

- AHB-AP thực hiện trao đổi dữ liệu với bộ nhớ hoặc thanh ghi và trả lại dữ liệu cho debug.

Serial – Wire or JTAG Debug Port (SW – DP or SWJ – DP)

Debug – Port là cổng giúp kết nối các công cụ debug với vi xử lý.

- SWJ – DP: cho phép chuyển đổi giữa hai chế độ: JTAG (nhiều chân hơn) với SW (ít chân kết nối hơn).

- SW – DP: sử dụng hai chân kết nối: clock và tín hiệu.

Icode và Dcode

Thông qua bus-matrix: Cortex-M3 processor core có thể kết nối đến:

- Icode:

- Là giao diện bus 32-bit thuộc loại AHB-Lite. Dùng để lấy cái lệnh (instruction) và dữ liệu từ vùng nhớ (từ địa chỉ 0x00000000 đến 0x1FFFFFFF).Mỗi lần lấy dữ liệu, ICode interface sẽ lấy theo từng từ (word).

- Đối với Thumb-2:

- Khi dữ liệu được định dạng theo kiểu word-aligned, câu lệnh Thumb-2 sẽ được trả về với một word.

- Khi dữ liệu được định dạng theo kiểu halfword aligned, khi lấy dữ liệu 32-bit, thì câu lệnh half-word được trả về đầu tiên, sau đó half-word tiếp theo sẽ được trả về để hoàn thành một word, điều này sẽ tạo ra một chu kỳ đợi (a wait cycle).

- Dcode:

- Là một giao diện bus 32-bit thuộc loại AHB-Lite, được sử dụng để truy cập dữ liệu và thực hiện gỡ lỗi trong vùng nhớ Code (từ địa chỉ 0x00000000 đến 0x1FFFFFFF).Khi có yêu cầu thực hiện truy cập dữ liệu và gỡ lỗi xảy ra đồng thời, thì việc truy cập dữ liệu sẽ được ưu tiên hơn.

- Nếu có truy cập dữ liệu không đúng vị trí, Dcode sẽ chia thành hai hoặc ba lần sao cho đúng vị trí, và các truy cập sau phải chờ cho đến khi hoàn tất.

Qua bài viết này, chúng ta đã khám phá kiến trúc của bộ xử lý ARM Cortex-M3. Bộ xử lý này nổi bật với hiệu suất cao và tính năng mạnh mẽ. Cortex-M3 được thiết kế cho ứng dụng nhúng đòi hỏi khả năng xử lý nhanh. Hy vọng bài viết giúp bạn hiểu thêm về bộ xử lý này. Hãy tiếp tục theo dõi chipstack.vn để không bỏ lỡ những bài viết bổ ích khác nhé!

Module chuyển đổi I2C cho LCD

Module chuyển đổi I2C cho LCD Hút thiếc

Hút thiếc