Tổng quan về Inter-Integrated Circuit (I2C) Để lại bình luận

Inter-integrated Circuit (I2C) là một giao thức bus tiêu chuẩn, ban đầu được phát triển bởi Philips vào cuối những năm 1980. Giao thức này cho phép các vi xử lý giao tiếp với các thiết bị ngoại vi bằng cách sử dụng hai dây: một dây dữ liệu nối tiếp (SDA) và một dây đồng hồ nối tiếp (SCL). Thiết kế hai dây này giúp giảm số lượng chân kết nối vật lý, làm cho việc giao tiếp trở nên rẻ và đơn giản.

Tốc độ truyền dữ liệu của I2C có thể đạt đến 100 Kbit/s ở chế độ tiêu chuẩn, lên đến 400 Kbit/s ở chế độ nhanh, và lên đến 3.4 Mbit/s ở chế độ cao tốc. Mỗi thiết bị trong hệ thống, bao gồm cả thiết bị chính và thiết bị ngoại vi, đều có một địa chỉ riêng biệt, thường là 7 bit, 10 bit hoặc 16 bit. Tùy theo chức năng, mỗi thiết bị có thể đóng vai trò là transmitter, receiver hoặc cả hai.

Master sẽ khởi tạo quá trình truyền dữ liệu trên bus, tạo ra tín hiệu xung clock để cho phép quá trình truyền dữ liệu, và kết thúc quá trình truyền sau khi nhận được tất cả thông tin yêu cầu. Thiết bị được địa chỉ hóa bởi master được gọi là slave. Nhiều master có thể cùng tồn tại trên cùng một bus I2C. Khi có nhiều master muốn điều khiển bus, sẽ thực hiện một quy trình tranh chấp quyền điều khiển (arbitration). Số lượng thiết bị kết nối với bus bị giới hạn bởi điện dung (capacitance) của bus.

Xem thêm: Hệ thống nhúng là gì?

Các chân của I2C

Một trong những nguyên nhân I2C phổ biến đó là do giao thức này chỉ sử dụng 2 chân: SDA và SCL.

- SCL (Serial Clock Line): Đây là đường dây clock nối tiếp, chủ yếu được điều khiển bởi master. SCL được dùng để đồng bộ hóa việc đọc hoặc ghi dữ liệu vào hoặc ra từ thiết bị đích.

- SDA (Serial Data Line): Đây là đường dây dữ liệu nối tiếp, dùng để gửi dữ liệu hoặc đọc dữ liệu từ các thiết bị slave.

Nói đơn giản, SCL giúp tạo nhịp để dữ liệu được truyền chính xác, còn SDA là đường dây mang dữ liệu giữa các thiết bị.

I2C là một kiểu giao tiếp bán song công (half-duplex), nghĩa là tại mỗi thời điểm chỉ có một thiết bị, dù là master hay slave, gửi dữ liệu trên bus. Điều này có nghĩa là dữ liệu chỉ có thể truyền theo một hướng tại một thời điểm, chứ không thể gửi và nhận đồng thời.

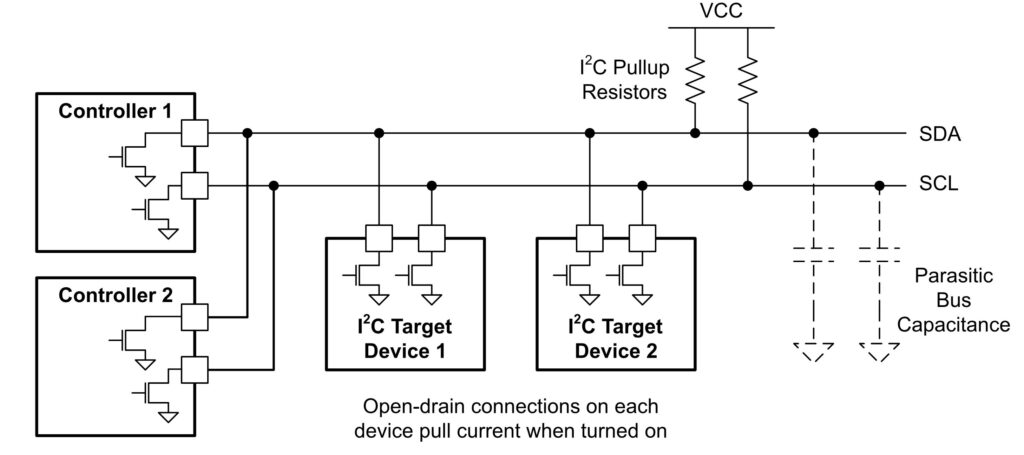

Các đường SDA và SCL trong giao tiếp I2C đều được kết nối theo kiểu “open-drain” đến tất cả các thiết bị trên bus. Các thiết bị chỉ có thể kéo mức điện áp xuống thấp (Logic 0), chứ không thể đưa điện áp lên mức cao (Logic 1). Vì vậy, cần sử dụng một điện trở kéo lên (pullup resistor) để kéo điện áp lên mức cao khi không có thiết bị nào kéo xuống mức thấp (Logic 0), đảm bảo tín hiệu trên bus luôn ổn định và rõ ràng.

Xem thêm: Open-drain và push-pull là gì?

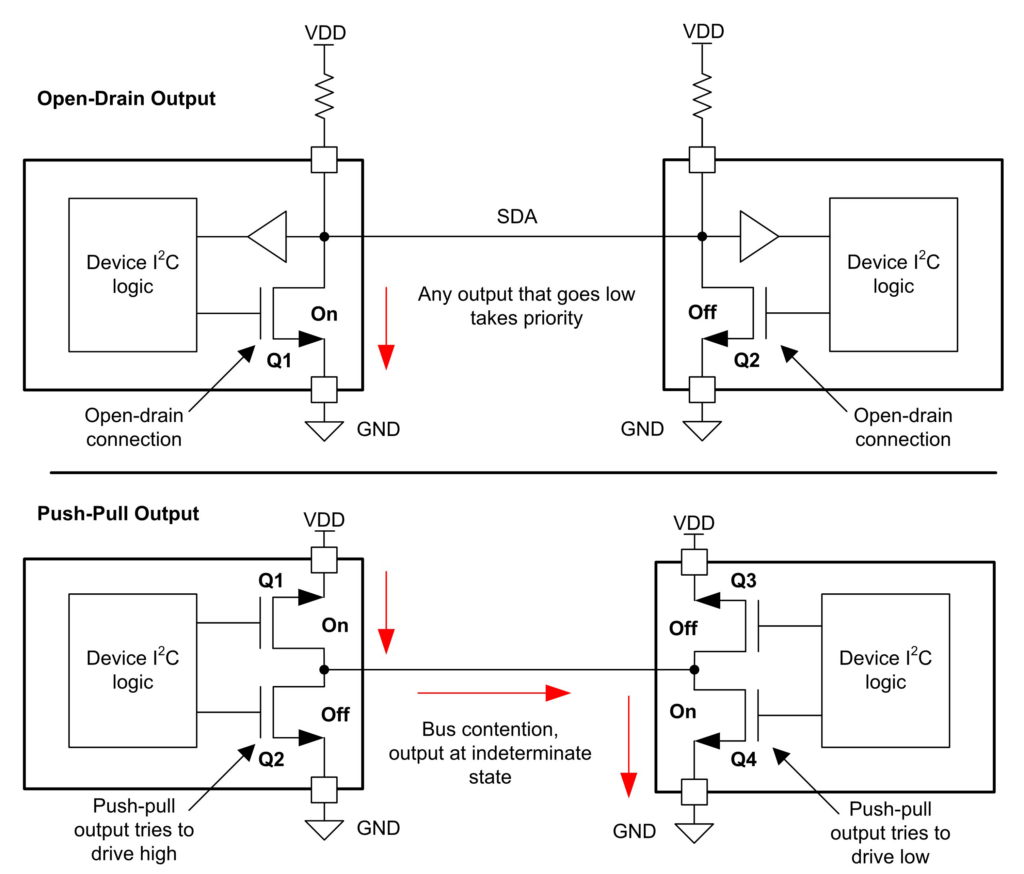

Vì sao I2C sử dụng Open-drain mà không phải là Push-pull?

Một lợi ích của việc sử dụng kết nối “open-drain” trong giao tiếp I2C là tránh được tình trạng ngắn mạch trên đường bus. Nhờ sử dụng wire-and, nếu có một thiết bị nào kéo xuống mức thấp (Logic 0) thì toàn bộ đường dây sẽ ở mức thấp (Logic 0).

Trong khi đó, nếu sử dụng đầu ra kiểu “push-pull” (thường dùng trong giao tiếp SPI), đầu ra được điều khiển bởi các transistor NMOS và PMOS bổ sung, có thể kéo mức điện áp lên cao hoặc xuống thấp. Nếu hai thiết bị cùng hoạt động trên bus với một thiết bị kéo lên cao và thiết bị kia kéo xuống thấp, sẽ xảy ra xung đột trên bus với trạng thái không xác định, có thể dẫn đến điện áp nằm giữa mức cao và mức thấp.

Trong trường hợp này, một thiết bị sẽ dẫn dòng từ VDD xuống GND qua đường dẫn có trở kháng rất thấp, dẫn đến dòng điện lớn chạy qua các transistor, gây ra ngắn mạch. Kết quả của sự xung đột này có thể là dòng điện lớn đủ để gây hỏng các thiết bị.

Hình 2 minh họa sự khác biệt giữa đầu ra open-drain và push-pull trong trường hợp có xung đột. Với kết nối open-drain, bất kỳ thiết bị nào cũng có thể kéo đường dây xuống thấp mà không gây ra tình trạng xung đột. Nhưng với kết nối push-pull, xung đột có thể dẫn đến trạng thái không xác định và thậm chí là hỏng hóc do dòng điện lớn.

Giao thức I2C

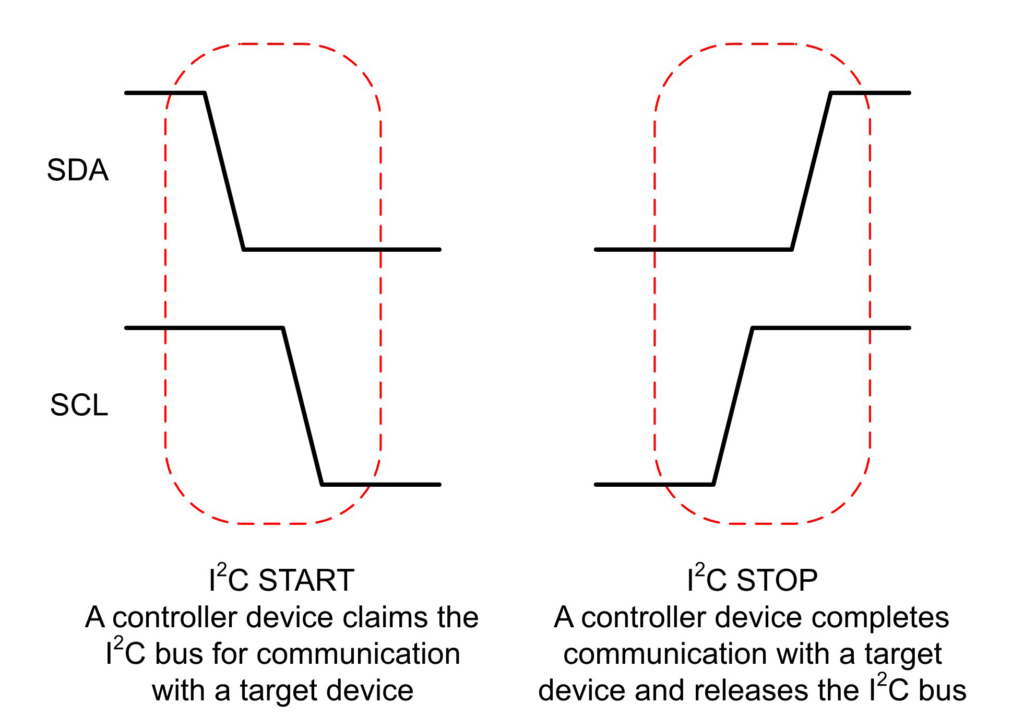

1. I2C START và STOP

Giao thức được bắt đầu với bit Start (S) và kết thúc với bit Stop (P).

Để bắt đầu giao tiếp, Master sẽ kéo SDA xuống mức thấp trước, sau đó sẽ kéo SCL xuống mức thấp, đây là điều kiện của bit Start (S).

Khi đã hoàn thành giao tiếp, SCL sẽ được Master thả lên mức cao trước , sau đó SDA cũng được thả lên mức cao, đây là điều kiện của bit Stop (P).

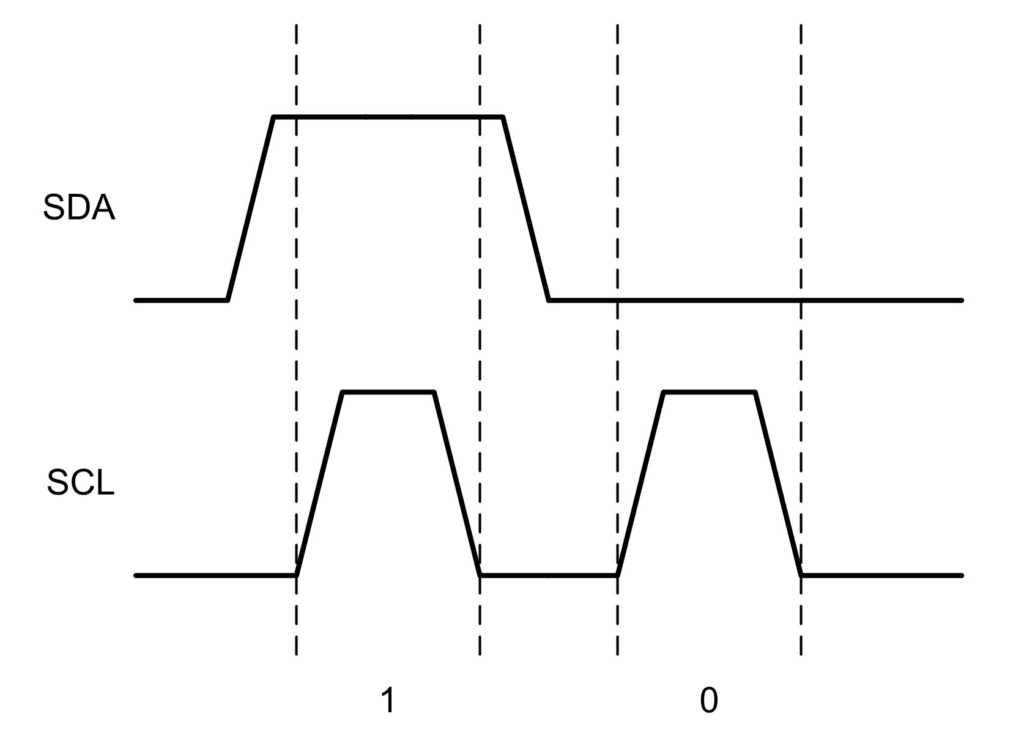

2. Logic 1 và Logic 0

I2C sử dụng chuỗi Logic 1 và logic 0 để giao tiếp nối tiếp. Trong giao tiếp I2C, SDA (Serial Data Line) được sử dụng để truyền các bit dữ liệu, còn SCL (Serial Clock Line) là đường dây xung clock dùng để đồng bộ hóa và xác định thời điểm các bit dữ liệu được gửi đi.

Logic 1 được gửi đi khi đường SDA được thả, cho phép pull-up resistor kéo SDA lên mức cao. Logic 0 được gửi đi khi đường SDA được kéo xuống mức thấp (điện áp gần với GND).

Trong hình 4, Các bit 0 và 1 nhận diện được khi trên đường SCL có xung. Để bit hợp lệ, SDA phải giữ nguyên giữa sườn lên và xuống của SC. Do đó sẽ không bị hiểu là bit START hay STOP.

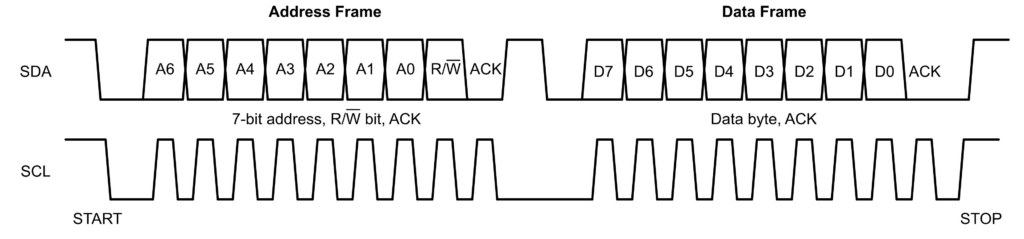

3. I2C Communication Frames

a. Address Frame

Giao thức I2C thường được chia thành nhiều Frame. Giao tiếp được bắt đầu khi Master gửi một Frame địa chỉ sau khi đã gửi Start bit. Sau một Frame địa chỉ là một hoặc nhiều Frame dữ liệu, mỗi Frame là một byte. Các Frame địa chỉ hay Frame dữ liệu có thêm một bit acknowledge để thông báo cho Master biết Slave hoặc Master khác đã nhận được thông tin địa chỉ hay dữ liệu.

Mỗi Slave đều có một địa chỉ I2C riêng biệt. Khi bắt đầu giao tiếp với một Slave cụ thể nào đó, Master sẽ sử dụng địa chỉ để phân biệt các Slave với nhau để gửi hoặc nhận dữ liệu.

Sau bit A0 (hình 5) là bit R/W. Nếu bit này là 1, Master yêu cầu đọc dữ liệu từ Slave. Nếu bit này là 0, Master sẽ yêu cầu ghi dữ liệu đến Slave.

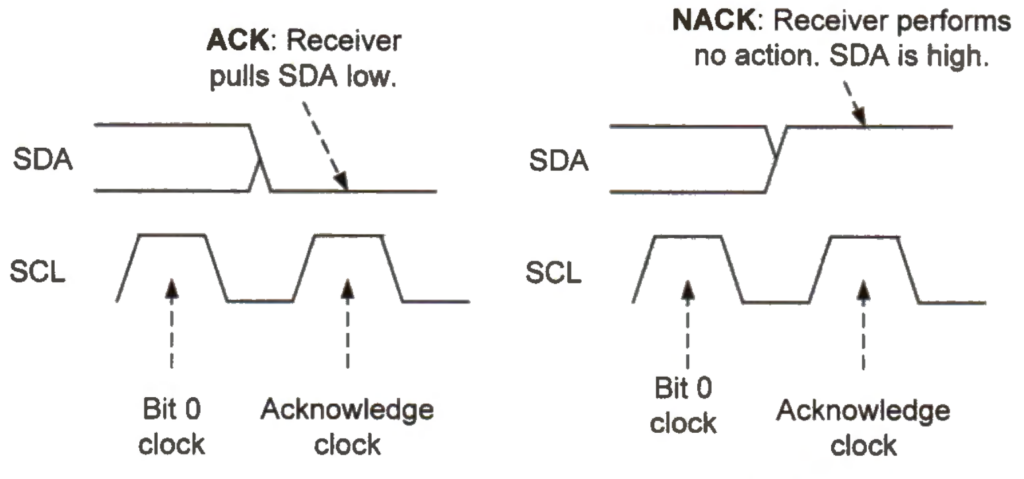

b. ACK và NACK

Sau byte địa chỉ, sẽ có một byte thứ 9 kèm thêm để xác định rằng giao tiếp đã xong hay chưa. Khi đó Master thả đường SDA ra để Slave kéo SDA xuống mức thấp, đây được gọi là bit ACK – chỉ ra rằng giao tiếp đã thành công. Nếu Slave không có phản hồi (không kéo SDA xuống mức thấp), bit này được gọi là bit NACK, do đó không có bất kỳ Slave nào nhận được địa chỉ vừa gửi đến dẫn đến giao tiếp không thành công.

Sau đó sẽ là các byte dữ liệu. Các Frame này được gửi mỗi byte một lần (byte by byte). Sau mỗi byte sẽ có thêm một bit ACK:

- Nếu Master ghi dữ liệu đến Slave, thì ở bit ACK, Slave sẽ kéo SDA xuống mức thấp để chỉ ra rằng dữ liệu đã được ghi thành công.

- Nếu Master đọc dữ liệu từ Slave, thì ở bit ACK, Master sẽ kéo SDA xuống mức thấp để chỉ ra rằng dữ liệu đã được đọc thành công.

- Còn nếu là bit NACK sẽ chỉ ra rằng giao tiếp đã không thành công hoặc Slave hay Master không muốn ghi/đọc dữ liệu nữa.

Nếu nhận bit NACK, Master gửi đi bit Stop bằng cách thả SCL lên mức cao sau đó sẽ thả SDA lên mức cao. Khi đó I2C hoàn thành giao tiếp và dừng lại.

Xem thêm: Tổng quan kiến trúc ARM-Cortex M3

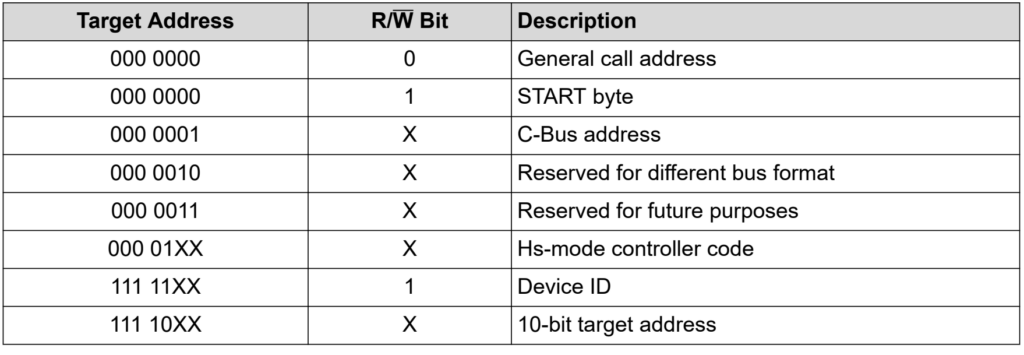

Reserved Addresses

Trong giao thức I2C, việc ghi và đọc từ thiết bị đích yêu cầu sử dụng một địa chỉ I2C. Địa chỉ này xác định thiết bị mà bộ điều khiển muốn giao tiếp. Thông thường, địa chỉ này được truyền dưới dạng một byte, trong đó 7 bit đầu là địa chỉ của thiết bị, và bit thứ tám được dùng để chỉ việc đọc hay ghi dữ liệu vào thiết bị.

Tuy nhiên, không phải tất cả các địa chỉ 7 bit đều có thể được sử dụng cho các thiết bị đích. Một số địa chỉ được dành riêng cho các mục đích khác, chẳng hạn như điều khiển bus I2C hoặc các chức năng đặc biệt khác. Những địa chỉ này không thể dùng cho các thiết bị ngoại vi thông thường.

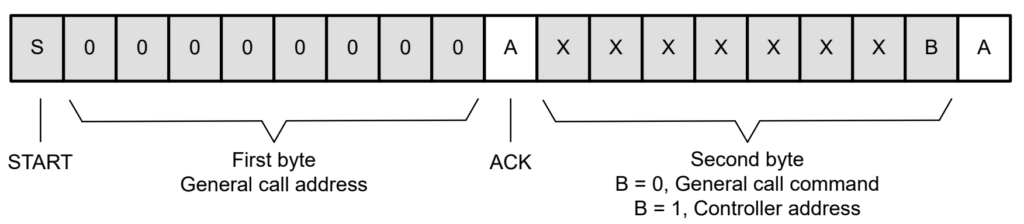

1. General call address

General Call trong giao thức I²C được sử dụng để gửi một lệnh đến tất cả các thiết bị trên bus I2C cùng lúc. Nó cho phép Master thực hiện các thao tác đồng thời trên tất cả thiết bị, mà không cần phải gửi lệnh riêng biệt cho từng thiết bị một.

Một số ứng dụng của General Call bao gồm:

- Reset tất cả các thiết bị: Ví dụ, gửi lệnh reset (byte 06h) để khởi động lại tất cả các thiết bị trên bus.

- Gửi lệnh chung: Các lệnh như “khởi động lại” hoặc “bắt đầu lại” có thể được gửi đến tất cả các thiết bị đồng thời.

Tuy nhiên, không phải tất cả các thiết bị Slave đều phản ứng với địa chỉ General Call, và nếu có Slave nào đó phản hồi thì byte thứ 2 có tác dụng dựa vào bit LSB (bit B):

- Nếu bit LSB (bit B) là 0: thì byte thứ 2 có thể được dùng để gửi tín hiệu reset cho toàn bộ Slave.

- Nếu bit LSB (bit B) là 1: giúp Master giao tiếp với Slave đó mà không cần biết địa chỉ của nó.

2. Start byte

START Byte là một byte đặc biệt với địa chỉ là 00 được sử dụng để bắt đầu giao tiếp trên bus I2C. Một số vi xử lý không có bộ điều khiển I2C tích hợp sẵn và không có interrupt để phát hiện giao tiếp, vì vậy phải liên tục kiểm tra tín hiệu SDA và SCL để phát hiện địa chỉ và giao tiếp. Điều này tiêu tốn năng lượng và tài nguyên xử lý.

Khi sử dụng START Byte, Slave có thể theo dõi bus ở tốc độ chậm, giúp tiết kiệm năng lượng. Sau khi phát hiện byte START với giá trị 0, thiết bị sẽ chuyển sang chế độ kiểm tra nhanh hơn để nhận địa chỉ và dữ liệu tiếp theo. Khi giao tiếp kết thúc với điều kiện STOP, thiết bị có thể lại chuyển sang chế độ kiểm tra chậm, tiết kiệm tài nguyên xử lý.

3. C-Bus Address, Different Bus Format, Future Purposes

Địa chỉ 01: Được dành riêng cho giao thức C-Bus, một giao thức dùng trong tự động hóa nhà và tòa nhà ở một số quốc gia, nhưng ít phổ biến ở Mỹ. Hầu hết các thiết bị I²C sẽ không phản hồi với địa chỉ này.

Địa chỉ 02: Dành cho các định dạng bus khác nhau, cho phép giao tiếp giữa các giao thức khác nhau. Chỉ những thiết bị I2C hỗ trợ giao tiếp giữa các giao thức khác nhau mới có thể phản hồi địa chỉ này.

Địa chỉ 03: Dành cho mục đích trong tương lai, chưa được xác định mục đích sử dụng địa chỉ này rõ ràng.

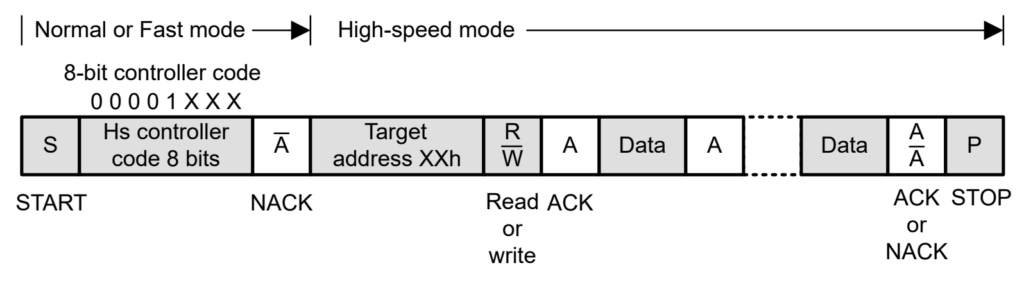

4. HS-Mode Controller Code

Các địa chỉ I²C từ 04 đến 07 được dành riêng cho mã điều khiển tốc độ cao (high-speed controller code). Những địa chỉ này không được sử dụng để xác định Slave mà chỉ dành cho các điều khiển tốc độ cao. Các mã điều khiển tốc độ cao này là các mã 8-bit, trong đó bit thứ tám, vốn được sử dụng cho bit R/W, sẽ được dùng để xác định mã điều khiển tốc độ cao.

Cách thức hoạt động:

- Bắt đầu: Thiết bị bắt đầu giao tiếp ở chế độ chuẩn hoặc nhanh. Bộ điều khiển gửi một START condition và gửi byte đầu tiên chứa mã điều khiển tốc độ cao.

- Kích hoạt tốc độ cao: Mã điều khiển này kích hoạt chế độ tốc độ cao cho tất cả Slave hỗ trợ chế độ này và bật các mạch nội bộ cần thiết để giao tiếp I²C nhanh hơn (so với chỉ dùng các điện trở pull-up).

- Tiếp tục truyền dữ liệu: Dữ liệu được truyền đi với ACK cho mỗi byte, giống như giao tiếp I²C tiêu chuẩn. Slave tiếp tục giao tiếp cho đến khi nhận được STOP condition hoặc START condition lặp lại cho một địa chỉ đích mới.

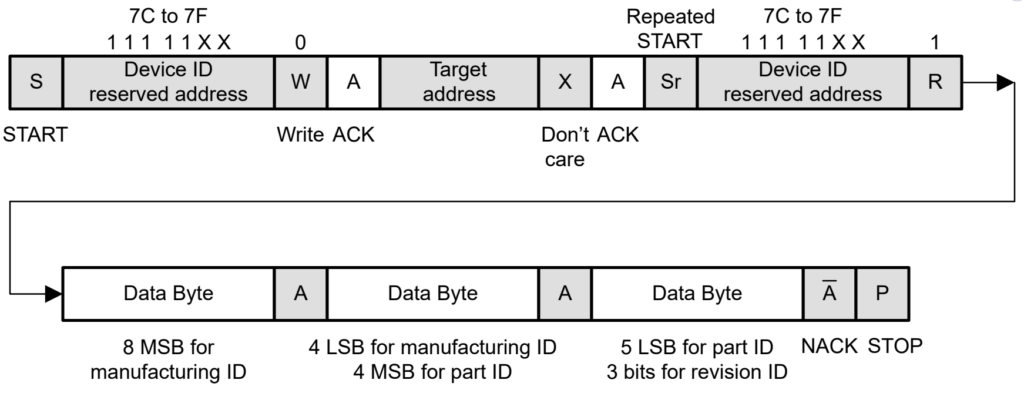

5. Device ID

Các địa chỉ I²C từ 7C đến 7F được dành riêng cho Device ID. Quá trình này giúp bộ điều khiển xác định và lấy thông tin về các thiết bị I²C kết nối trong hệ thống thông qua Device ID.

Cách thức hoạt động:

- Gửi địa chỉ Device ID: Master bắt đầu bằng cách gửi địa chỉ Device ID theo sau là bit ghi (write bit).

- Gửi địa chỉ thiết bị Slave: Master tiếp tục gửi địa chỉ của Slave để nhận diện.

- Repeated START condition: Sau đó, Master gửi một repeated START condition, tiếp theo là địa chỉ Device ID với bit đọc (read bit).

- Truyền Device ID: Slave gửi lại Master 3 byte dữ liệu gồm:

- 12 bit cho manufacturer ID (mã nhà sản xuất),

- 9 bit cho part identification (mã nhận diện bộ phận),

- 3 bit cho die revision (phiên bản của chip).

- Kết thúc đọc: Master gửi bit NACK cho byte cuối cùng và kết thúc việc đọc Device ID bằng STOP condition. Việc đọc có thể dừng bất kỳ lúc nào bằng cách gửi NACK.

6. 10-Bit Target Addressing

Để mở rộng số lượng thiết bị I2C có thể kết nối trên một bus, I2C sử dụng địa chỉ 10-bit thay vì chỉ 7-bit.

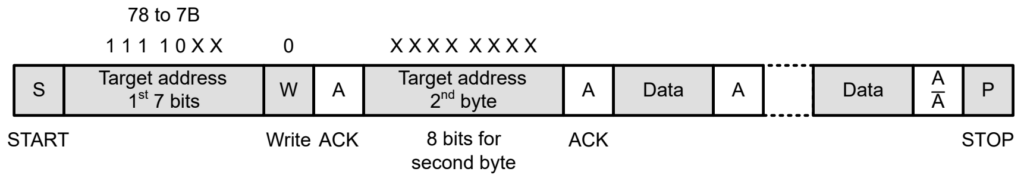

a. 10-Bit Target Addressing Write

Slave gửi tín hiệu START để bắt đầu quá trình giao tiếp.

Byte đầu tiên được gửi có một phần là địa chỉ dành riêng cho giao thức I²C 10-bit (gọi là “reserved address”). Byte này bao gồm:

- 5 bit đầu tiên là giá trị cố định để xác định rằng đây là giao tiếp sử dụng địa chỉ 10-bit.

- 2 bit tiếp theo là 2 bit cao nhất của địa chỉ 10-bit.

- Bit cuối cùng là 0, biểu thị đây là một yêu cầu ghi dữ liệu (write).

Lúc này có thể có nhiều thiết bị khác nhau phản hồi (ACK) vì các thiết bị có cùng “reserved address” và 2 bit đầu tiên của địa chỉ 10-bit. Do đó ta cần gửi byte địa chỉ thứ 2.

Byte này chứa 8 bit còn lại (gọi là 8 bit thấp) của địa chỉ 10-bit của thiết bị đích. Dựa trên thông tin đầy đủ từ byte đầu tiên (gồm 2 bit cao) và byte thứ hai (gồm 8 bit thấp) tổng cộng là 10 bit, do đó chỉ có một thiết bị duy nhất có địa chỉ trùng khớp sẽ phản hồi (ACK).

Sau khi nhận diện đúng thiết bị, quá trình truyền dữ liệu giữa Master và Slave sẽ diễn ra:

- Master tiếp tục gửi dữ liệu.

- Quá trình này duy trì cho đến khi Master gửi tín hiệu STOP hoặc Repeated START để chuyển sang Slave khác.

Xem thêm: Xung clock là gì?

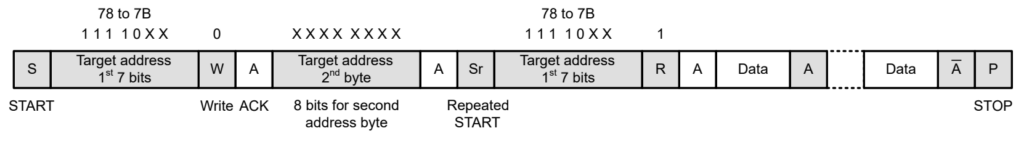

b. 10-Bit Target Addressing Read

START: Master gửi tín hiệu START để bắt đầu giao tiếp.

Gửi byte đầu tiên, byte này chứa:

- Địa chỉ dành riêng cho giao thức 10-bit (reserved address).

- 2 bit cao của địa chỉ 10-bit.

- Bit ghi (write bit) là 0 (để thông báo đây là bước ghi).

- ACK đầu tiên: Tất cả các thiết bị có cùng địa chỉ “reserved” và 2 bit cao sẽ phản hồi (ACK).

- Gửi byte thứ hai: Gửi 8 bit thấp của địa chỉ 10-bit (để xác định chính xác thiết bị).

- ACK từ Slave: Chỉ thiết bị có địa chỉ khớp hoàn toàn (2 bit cao + 8 bit thấp) phản hồi (ACK).

Và để đọc được dữ liệu từ Slave, Master gửi một bit Repeated START mới có thể gửi bit đọc được.

Gửi byte đầu tiên lại: Gửi lại byte đầu tiên, gồm:

- Địa chỉ “reserved” + 2 bit cao của địa chỉ 10-bit.

- Bit đọc (read bit) là 1.

Tại sao lại gửi byte này? Vì byte này bao gồm bit đọc nên ta cần phải gửi byte này.

Sau đó bit ACK từ Slave sẽ được trả về.

Cuối cùng thực hiện giao tiếp như bình thường:

Slave bắt đầu truyền dữ liệu (byte đầu tiên) cho bộ điều khiển.

ACK từ Master gửi tới xác định đã đọc thành công.

Khi không muốn đọc dữ liệu nữa, Master gửi bit Nack tới Slave và gửi tín hiệu STOP. Hoặc, nếu cần chuyển sang thiết bị khác, Master gửi một tín hiệu Repeated START và lặp lại quy trình trên với địa chỉ mới.

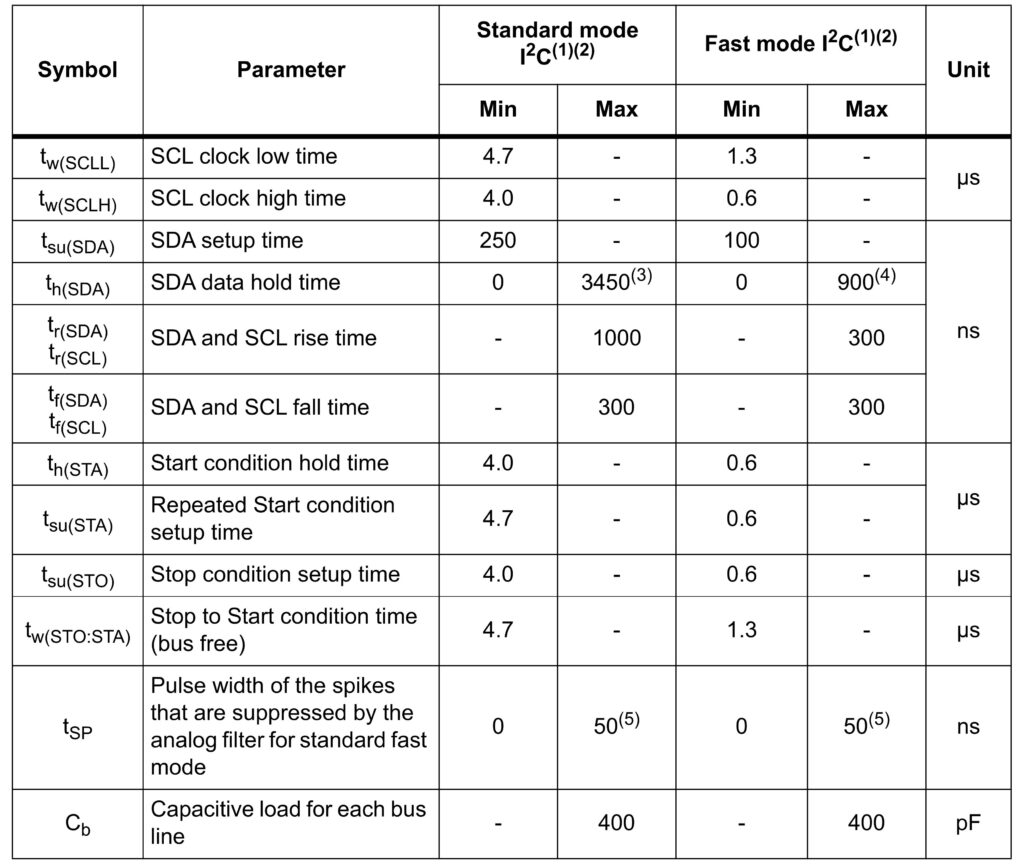

Tính toán tốc độ của I2C

Để thiết kế hệ thống sao cho tốc độ bus đủ nhanh đáp ứng được yêu cầu của giao thức I²C, bạn cần tính toán giá trị của các điện trở kéo lên (pull-up resistors).

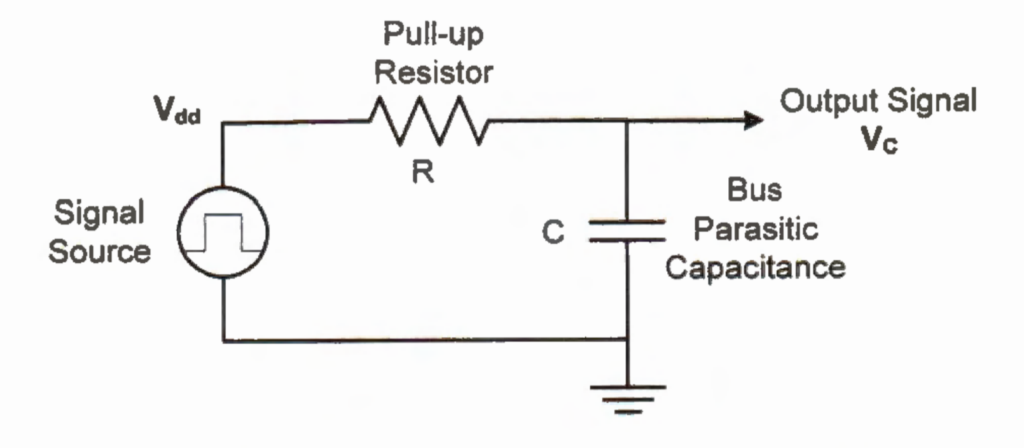

Trong kết nối open-drain của các đường SDA (Data) và SCL (Clock), quá trình chuyển mức từ cao xuống thấp (high to low) và từ thấp lên cao (low to high) phụ thuộc vào các yếu tố sau:

- Dòng điện do thiết bị với kết nối open-drain cung cấp (dòng điện kéo xuống – current sink).

- Điện dung trên bus (bus capacitance), bao gồm điện dung từ dây dẫn và các thiết bị kết nối vào bus.

- Giá trị của điện trở kéo lên (pull-up resistor).

Trong giao thức I²C, điện trở kéo lên (pullup resistor) đóng vai trò quan trọng trong việc duy trì mức logic cao trên các đường SDA và SCL khi không có thiết bị nào kéo xuống.

Khoảng giá trị khuyến nghị: Điện trở kéo lên thường nằm trong khoảng 1 kΩ đến 10 kΩ. Giá trị này được chọn dựa trên sự cân bằng giữa tốc độ truyền dữ liệu và mức tiêu thụ điện năng:

- Điện trở cao hơn (gần 10 kΩ): Giảm tiêu thụ điện năng nhưng làm chậm tốc độ giao tiếp I²C.

- Điện trở thấp hơn (gần 1 kΩ): Tăng tốc độ giao tiếp nhưng tiêu thụ nhiều năng lượng hơn.

1. Điện dung trên bus

Khi có hai dây dẫn được cách điện và có một hiệu điện thế giữa chúng, chúng sẽ tạo thành một tụ điện. Trên mạch in (PCB), các đường dẫn điện, dây nối, chân linh kiện… đều có một loại điện dung tự nhiên gọi là điện dung ký sinh. Điện dung này rất nhỏ, nhưng nếu tín hiệu chạy trên mạch có tần số cao (như trong giao thức I²C), nó có thể làm tín hiệu chậm lại hoặc gây nhiễu.

Điện dung của bus là tổng của các điện dung ký sinh của dây dẫn, chân linh kiện…

Từ hình 14, ta có thể thấy rằng tổng điện dung tối đa cho phép đối với I2C là 400pF, điều này làm giới hạn số lượng thiết bị I2C kết nối trên cùng một bus.

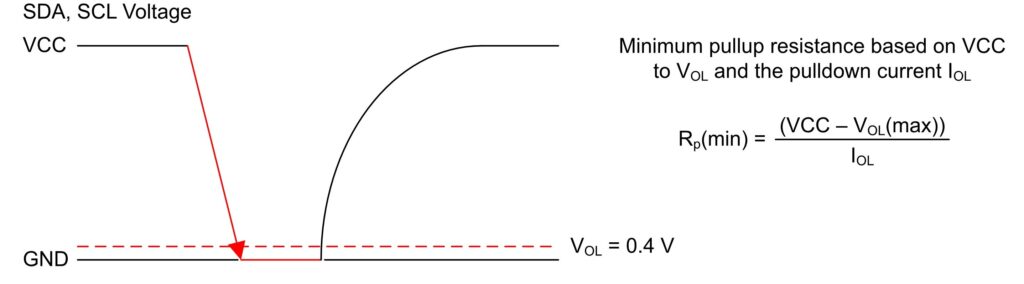

2. Tính điện trở kéo lên tối thiểu

Ta có công thức tính điện trở kéo xuống tối thiểu:

Trong đó:

VCC là điện áp cung cấp (3.3V).

Điện áp thấp (VOL): Là mức điện áp thấp mà đường bus có thể đạt được khi bị kéo xuống. Trong ví dụ này, VOL là 0.4V.

Dòng điện kéo xuống (IOL): Là dòng điện mà thiết bị có thể kéo xuống. Trong ví dụ, dòng điện này là 3mA.

Kết quả: Điện trở kéo lên tối thiểu cần thiết là 967 Ω. Nếu sử dụng điện trở nhỏ hơn giá trị này, dòng điện không đủ để kéo mức điện áp bus xuống mức thấp (VOL), gây ra lỗi trong giao tiếp.

Xem thêm: Ngắt là gì?

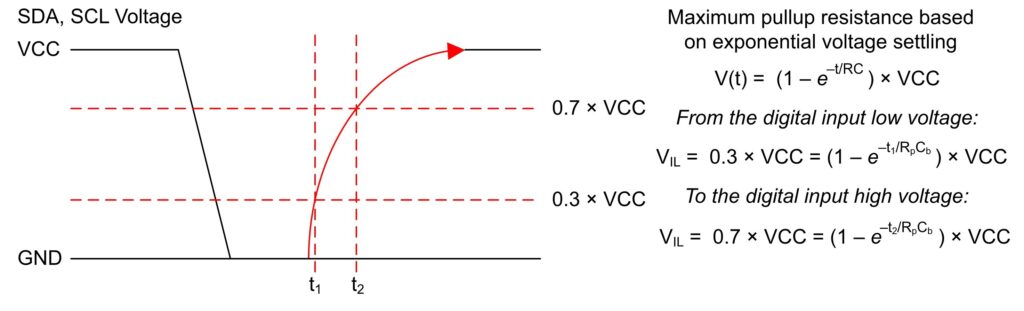

3. Tính toán điện trở kéo lên tối đa

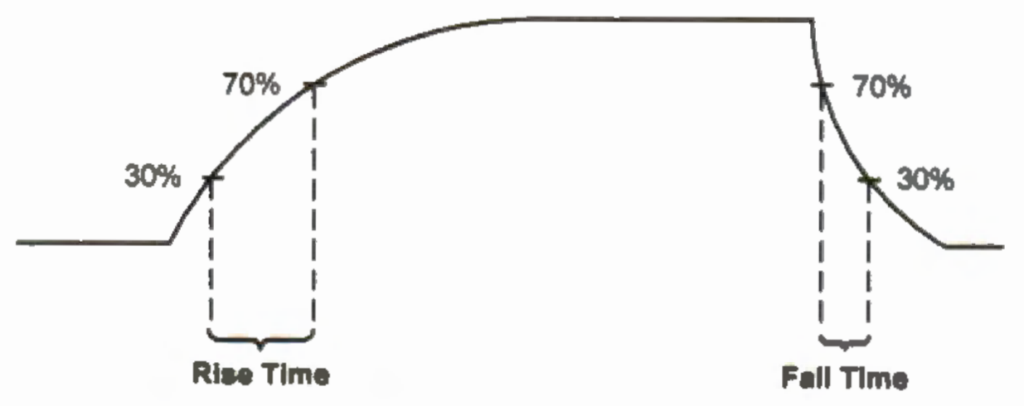

Thời gian tăng (rise time) là khoảng thời gian cần thiết để tín hiệu điện áp tăng từ mức thấp lên mức cao. Thời gian tăng 30-70% là thời gian tín hiệu tăng từ 30% đến 70% giá trị điện áp cuối cùng.

Thời gian giảm (fall time) là thời gian tín hiệu giảm từ 70% xuống 30% giá trị cuối cùng.

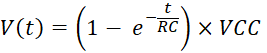

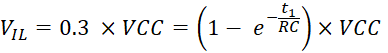

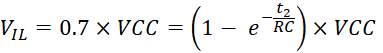

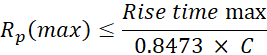

Trong giao thức I²C, khi kết nối open-drain không còn kéo xuống, các điện trở kéo lên (pullup resistors) sẽ kéo điện áp trên đường bus lên mức cao. Quá trình này không xảy ra ngay lập tức mà có dạng sóng đầu ra tăng dần theo đường cong hàm mũ (exponential settling) vì điện dung trên bus cần thời gian để sạc đầy theo hình 18, do đó thời gian khi kéo lên thường dài hơn thời gian khi kéo xuống do khi kéo xuống transistor bên trong được bật và nối với GND trực tiếp.

Do phụ thuộc vào điện dung, nên công thức tổng quát của điện trở tối đa là:

Tại mức tín hiệu thấp là 0.3 (30%) ở thời điểm t1:

Do đó, t1 = 0.3567 x RC.

Tại mức tín hiệu cao là 0.7 (70%) ở thời điểm t2:

Do đó, t2 = 1.2040 x RC.

Vậy ta tính được Rise time = t2 – t1 = 0.8473 x RC.

Do đó, điện trở kéo lên tối đa được chọn sao cho Rise time = 0.8473 x RC <= Rise time max với Rise time max được cho theo datasheet của nhà sản xuất.

Vậy điện trở kéo lên tối đa được tính theo công thức:

Clock Synchronization và Arbitration

1. Clock synchronization

Trong I2C, Có thể có nhiều Master trên cùng một bus. Do đó, có thể có hai hoặc ba Master cố gắng chiếm quyền giao tiếp trên bus đó ở cùng thời điểm. Điều này yêu cầu nhiều Master hoạt động cùng lúc để xác định thiết bị nào quyết định đường truyền dữ liệu (bus).

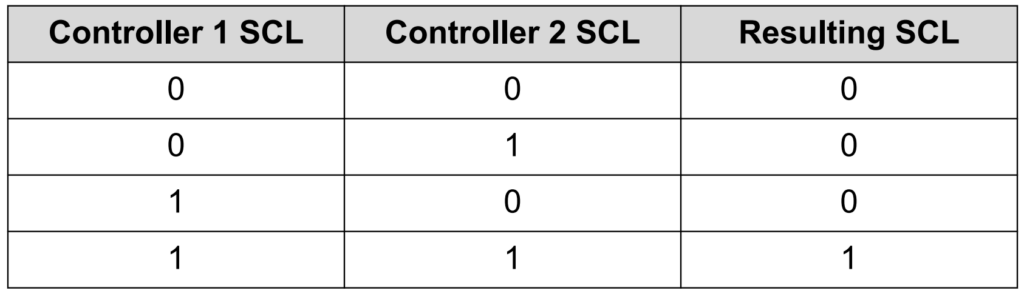

Do I2C sử dụng kiểu kết nối open-drain ở SDA và SCL, điều này tạo ra kiểu kết nối wired-And, do đó sẽ tạo ra kiểu logic AND.

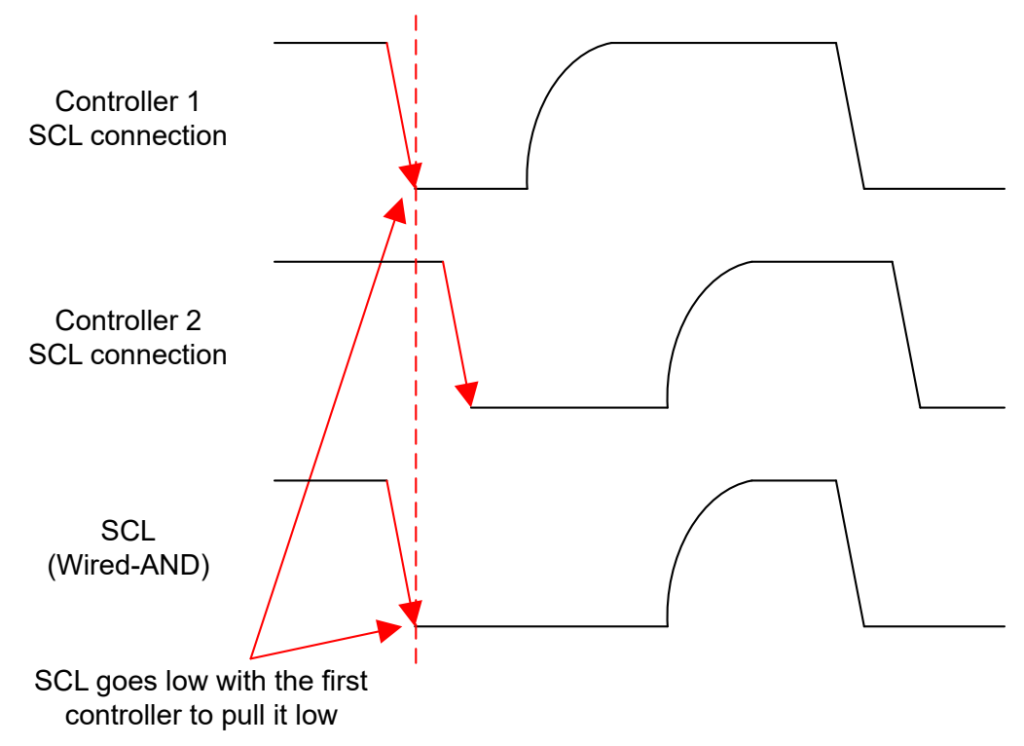

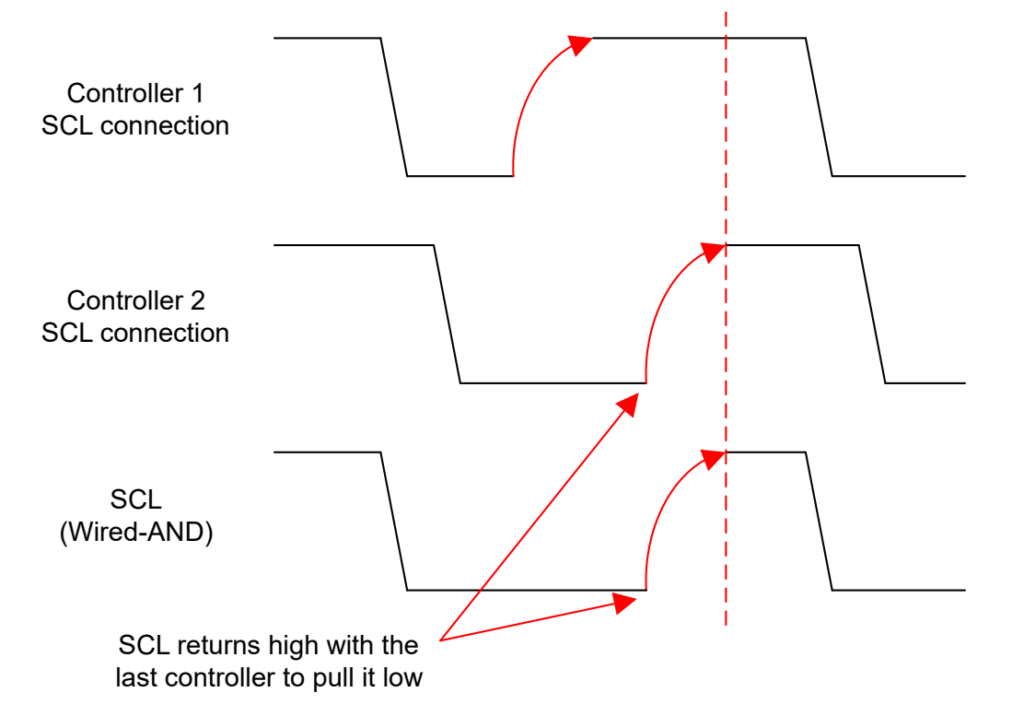

Ở hình 20, 2 Master đang khởi tạo bit START, Master 1 kéo xuống mức thấp trước Master 2. Với kiểu kết nối AND, SCL sẽ được kéo xuống mức thấp ngay khi Master 1 kéo xuống mức thấp mà không cần Master 2 kéo xuống mức thấp.

Sau đó Master 1 thả lên mức cao nhưng do Master 2 vẫn giữ ở mức thấp nên SCL vẫn ở mức thấp. Do đó Master 1 chờ cho đến khi Master 2 thả lên mức cao do đó SCL sẽ ở mức cao.

Do đó, SCL sẽ ở mức thấp cho đến khi không còn Master nào kéo xuống mức thấp.

Mức thấp của SCL clock được xác định bởi Master có mức thấp dài nhất. Mức cao của SCL clock được xác định bởi mức cao ngắn nhất của Master. Đó được gọi là Clock Synchronization.

2. Atribation

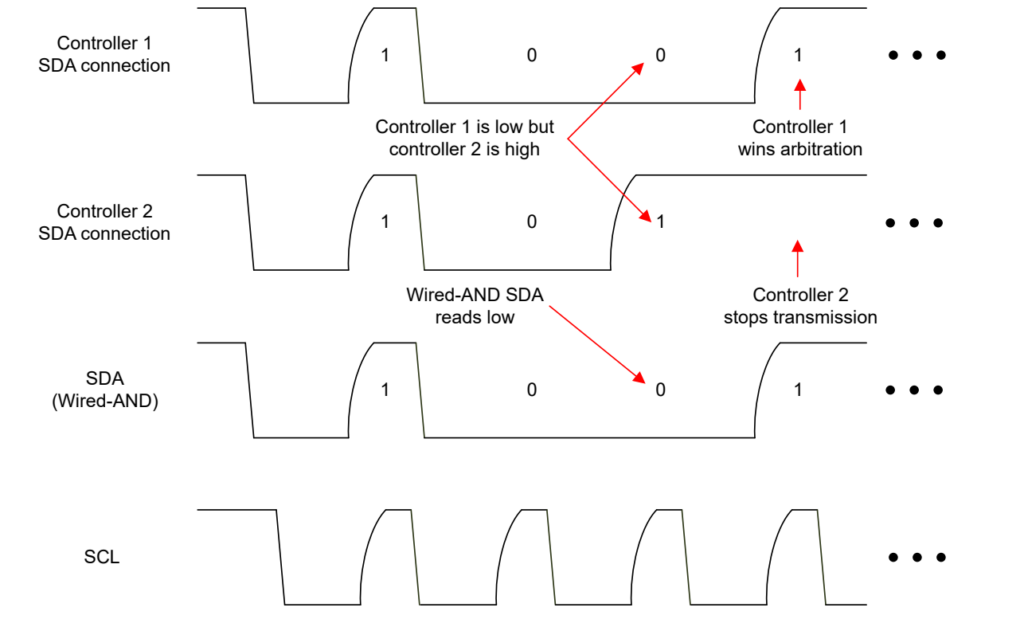

Atribation được thực hiện trên SDA. Tương tự như SCL, SDA cũng được kết nối theo kiểu wired-And.

Ở hình 22, Ở 2 bit đầu thì Master 1 và Master 2 đều gửi bit giống nhau, ở bit thứ 3 Master 1 gửi bit 0 trong khi Master 2 gửi bit 1, theo logic AND thì Master 1 sẽ được ưu tiên và chiếm quyền giao tiếp, do đó để tránh xung đột thì Master 2 sẽ ngừng gửi dữ liệu.

Xem thêm: Run mode và low power mode là gì?

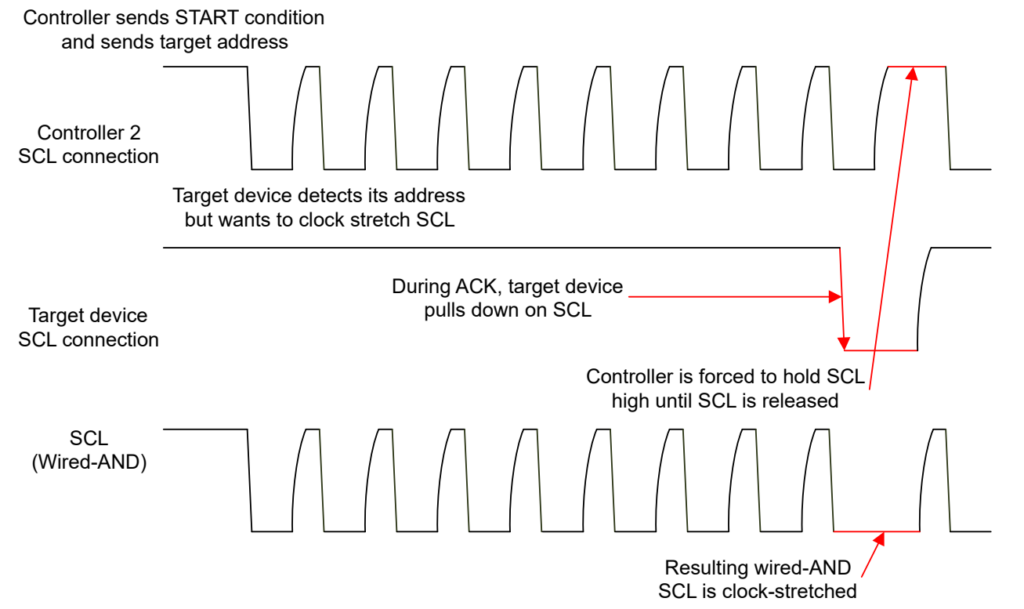

Clock Stretching

Trong một số thiết bị Slave, có những tình huống mà thiết bị Slave kiểm soát xung nhịp SCL. Trong các trường hợp này, thiết bị Slave có thể làm chậm quá trình giao tiếp. Quá trình này được gọi là clock stretching. Điều này thường xảy ra ở bit ACK.

Khi ở bit ACK, Slave sẽ điều khiển SCL và SDA trong khi Master đã thả ở mức cao, ví dụ khi cần thêm thời gian để xử lý lệnh hoặc gửi dữ liệu, Slave sẽ kéo đường SCL xuống mức thấp. Do đó việc giao tiếp tạm thời dừng lại để Slave có thời gian chuẩn bị dữ liệu cho đến khi đường SCL được thả lên mức cao.

Xem thêm: Tổng quan về GPIO

I2C, với thiết kế hai dây đơn giản, đã trở thành một giao thức giao tiếp phổ biến nhờ khả năng tiết kiệm chân kết nối và dễ dàng tích hợp nhiều thiết bị trên cùng một bus. Sự kết hợp giữa các đường dây open-drain và các kỹ thuật truyền dữ liệu như arbitration giúp giao thức này ổn định và hiệu quả, đặc biệt trong các hệ thống có nhiều master và slave.