Tổng số phụ: 47.023 ₫

Analog-to-Digital Converter (ADC): Nguyên lý và Ứng dụng Để lại bình luận

Bộ chuyển đổi tương tự sang số (ADC) là một linh kiện giúp biến đổi tín hiệu điện áp tương tự (analog) thành một giá trị số (digital) có độ chính xác hữu hạn. Giá trị số này có thể ở dạng số nguyên có dấu hoặc không dấu, và nó thể hiện gần đúng mức điện áp đầu vào so với một mức điện áp tham chiếu.

Điện áp tham chiếu (Vref) là một mức điện áp cố định được cung cấp bởi vi điều khiển hoặc một mạch bên ngoài. Điện áp đầu vào cần đo phải nằm trong phạm vi từ 0V đến Vref. Nếu điện áp đầu vào lớn hơn Vref, ADC không thể đo chính xác giá trị đó.

3 thông số quan trọng của ADC

🔹 Tốc độ lấy mẫu (Sampling rate): ADC có thể lấy mẫu từ vài nghìn đến hàng triệu, thậm chí hàng tỷ lần mỗi giây (MSPS – Mega Samples Per Second, GSPS – Giga Samples Per Second). Đây là số lần ADC thực hiện phép đo trong một giây.

🔹 Độ phân giải (Resolution): Độ phân giải của ADC được đo bằng số bit của giá trị đầu ra. ADC 8-bit có thể biểu diễn 256 mức khác nhau. ADC 12-bit có thể biểu diễn 4096 mức khác nhau. ADC 24-bit có thể biểu diễn hơn 16 triệu mức khác nhau. Mặc dù có ADC lên đến 24-bit, nhưng hầu hết các ứng dụng chỉ cần 12-bit hoặc 16-bit là đủ.

🔹 Công suất tiêu thụ (Power dissipation): Đây là lượng điện năng mà ADC tiêu thụ khi hoạt động. Trong các hệ thống nhúng di động (như điện thoại, cảm biến không dây), công suất tiêu thụ là yếu tố quan trọng hơn cả tốc độ ADC, vì thiết bị cần tiết kiệm năng lượng để kéo dài thời gian sử dụng pin.

Kiến trúc ADC

Có ba kiến trúc ADC phổ biến nhất: sigma-delta ADC dành cho các ứng dụng tốc độ thấp, successive-approximation (SAR) ADC cho các ứng dụng tiêu thụ ít năng lượng, và pipelined ADC cho các ứng dụng tốc độ cao.

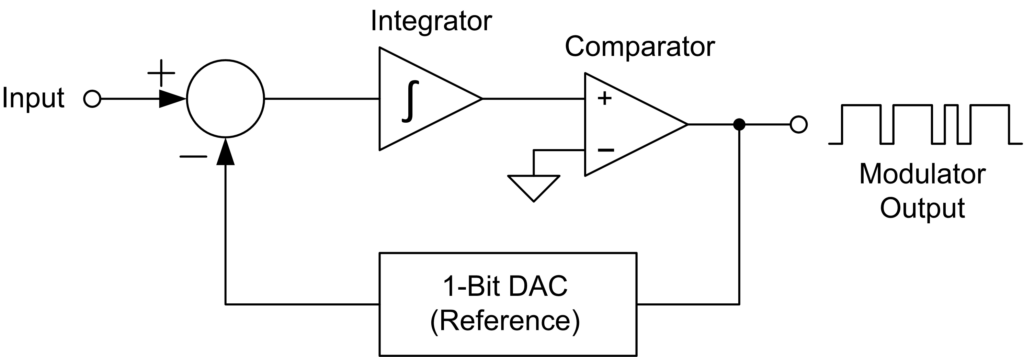

1. Sigma-Delta ADC

Thường được sử dụng khi cần tốc độ lấy mẫu thấp (dưới 100k mẫu/giây) nhưng độ phân giải cao (12–24 bit).

Ứng dụng phổ biến trong âm thanh và băng thoại, ví dụ như trong điện thoại di động.

Xem thêm: Controller Area Network (CAN) bus – Hệ Thần Kinh Của Ô Tô Hiện Đại

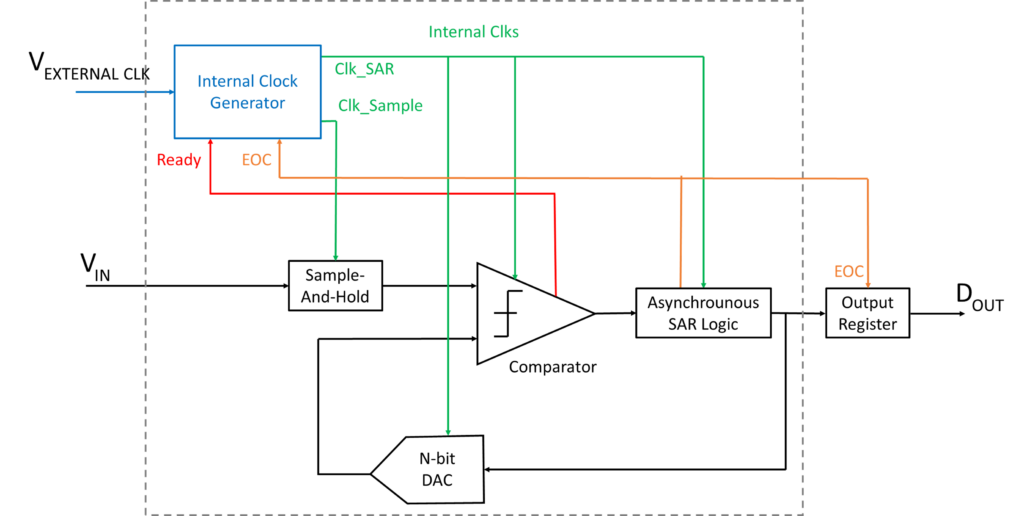

2. SAR ADCs

Phù hợp với các hệ thống thu thập dữ liệu có mức tiêu thụ điện năng thấp.

Tốc độ lấy mẫu trung bình (dưới 5 triệu mẫu/giây – 5 MSPS).

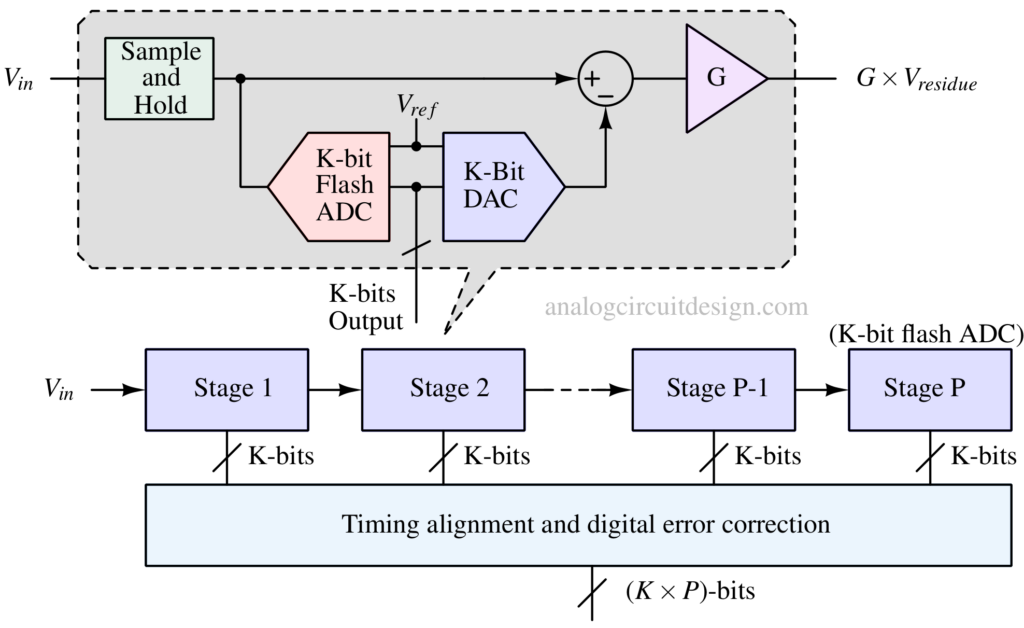

3. Pipelined ADCs

Thường được dùng trong các thiết bị cần tốc độ lấy mẫu cao (trên 5 MSPS) nhưng độ phân giải không quá cao (dưới 18 bit).

Ứng dụng phổ biến trong máy hiện sóng số, HDTV, và radar.

Trên vi điều khiển STM32, ADC sử dụng kiến trúc SAR, bao gồm hai thành phần chính:

🔹 Bộ khuếch đại giữ mẫu (Sample-and-Hold Amplifier – SHA) để lấy và giữ tín hiệu đầu vào.

🔹 Bộ số hóa SAR để chuyển đổi tín hiệu tương tự sang số theo phương pháp xấp xỉ liên tiếp.

Lượng tử hóa số (Digital Quantization)

Quá trình lượng tử hóa số trong ADC SAR hoạt động dựa trên thuật toán tìm kiếm nhị phân, nhằm tìm ra giá trị số gần nhất với tín hiệu đầu vào tương tự. Nguyên tắc hoạt động như sau:

1. Bắt đầu chuyển đổi

- Bộ điều khiển SAR đặt điện áp đầu ra của DAC nội bộ (Vdac) bằng VREF/2 (tức là một nửa điện áp tham chiếu).

- So sánh Vdac với điện áp đầu vào Vin.

2. So sánh và xác định bit cao nhất (MSB – Most Significant Bit)

- Nếu Vin > Vdac, SAR sẽ đặt bit cao nhất (MSB) = 1.

- Nếu Vin < Vdac, SAR sẽ đặt bit cao nhất = 0.

3. Lặp lại quá trình tìm kiếm nhị phân

- Tiếp tục điều chỉnh Vdac bằng cách giảm phạm vi giá trị dựa trên bit đã đặt.

- Ví dụ, nếu MSB = 1, Vdac sẽ tăng lên 3/4 VREF; nếu MSB = 0, Vdac sẽ giảm xuống 1/4 VREF.

- Quá trình này lặp lại cho tất cả các bit tiếp theo.

4. Hoàn tất chuyển đổi

- Nếu ADC có độ phân giải n bit, thì quá trình chuyển đổi cần n bước để xác định giá trị số đầu ra.

- Độ phân giải càng cao, thời gian chuyển đổi càng lâu, kết quả càng chính xác. Vì vậy có sự đánh đổi giữa độ phân giải và tốc độ lấy mẫu.

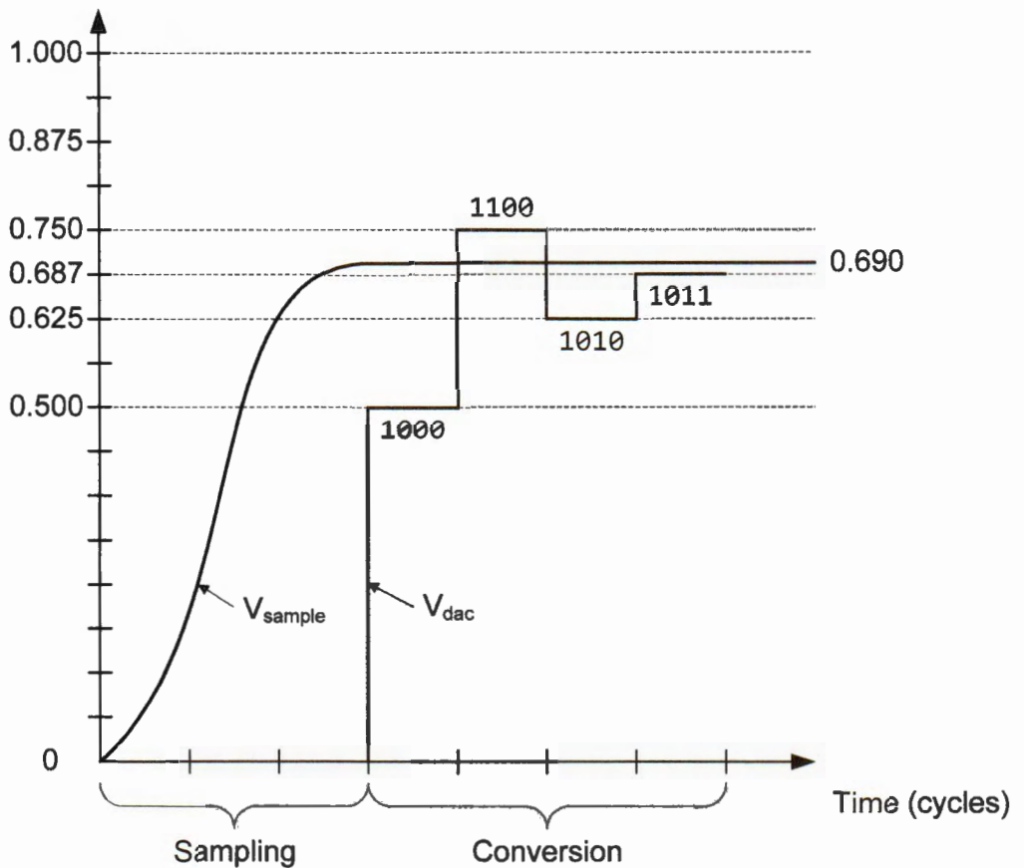

Ví dụ: Chuyển đổi điện áp 0.690V với ADC SAR 4-bit:

Giả sử phạm vi điện áp đầu vào là 0V – 1V, ta có quy trình chuyển đổi như sau:

🔹 Bước 1: Đặt Vdac = 0.500V (ADC = 1000) → Vin (0.690V) > Vdac, nên đặt MSB = 1.

🔹 Bước 2: Đặt Vdac = 0.750V (ADC = 1100) → Vin < Vdac, nên bit tiếp theo là 0.

🔹 Bước 3: Đặt Vdac = 0.625V (ADC = 1010) → Vin > Vdac, nên bit tiếp theo là 1.

🔹 Bước 4: Đặt Vdac = 0.687V (ADC = 1011) → Vin > Vdac, nên bit cuối cùng là 1.

Kết quả: Điện áp 0.690V được mã hóa thành 0b1011 (4-bit) trong 4 chu kỳ.

Xem thêm: Hiểu về Direct Memory Access (DMA)

Lấy mẫu và giữ (Sampling and Hold)

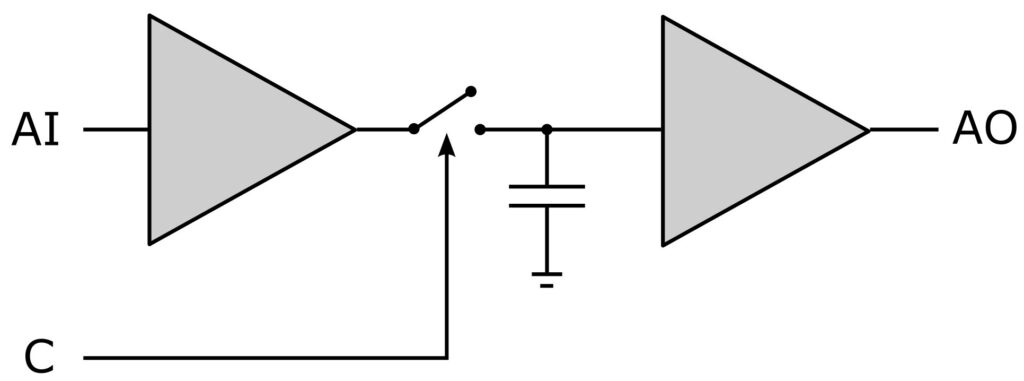

1. Cách hoạt động của mạch Sample-and-Hold

Mạch này bao gồm:

🔹 Một công tắc điện tử (switch) – dùng để đóng/mở lấy mẫu.

🔹 Một tụ điện (capacitor) – dùng để lưu trữ giá trị điện áp.

🔹 Một bộ khuếch đại (op-amp) – giúp duy trì giá trị điện áp ổn định.

Cơ chế hoạt động:

Lấy mẫu (Sampling):

🔹 Khi công tắc đóng, tụ điện bắt đầu nạp điện theo điện áp đầu vào Vin.

🔹 Nhưng do tính chất RC (điện trở & tụ điện), điện áp trên tụ không thay đổi ngay lập tức mà tăng theo hàm mũ.

Giữ giá trị (Hold):

🔹 Khi công tắc mở, tụ điện giữ nguyên điện áp hiện tại, giúp ADC có thời gian để thực hiện chuyển đổi.

🔹 Sau đó, ADC đọc giá trị này và thực hiện chuyển đổi sang dạng số.

Xem thêm: Quad Serial Peripheral Interface (Quad-SPI) là gì?

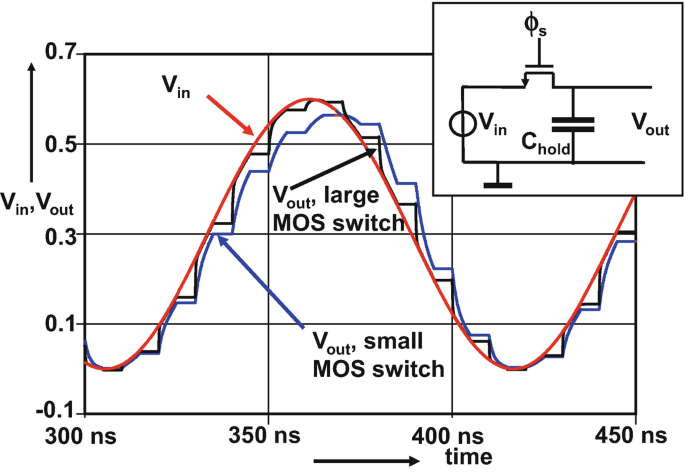

2. Tại sao cần thời gian lấy mẫu đủ dài?

Vì điện áp trên tụ không thể thay đổi ngay lập tức, nên nếu thời gian lấy mẫu quá ngắn, tụ chưa kịp đạt đến giá trị Vin thực sự.

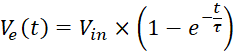

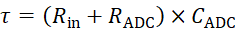

Công thức:

Với:

Ví dụ:

🔹 Nếu thời gian lấy mẫu bằng 3τ, điện áp trên tụ mới đạt 95% giá trị thực của Vin.

🔹 Nếu muốn chính xác hơn (ví dụ 99%), cần thời gian lấy mẫu khoảng 5τ.

Vậy nên: Nếu thời gian lấy mẫu quá ngắn, ADC sẽ đọc sai giá trị.

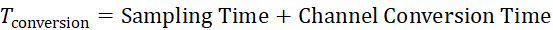

3. Cách tính thời gian chuyển đổi ADC trên vi điều khiển

Tổng thời gian chuyển đổi ADC được tính như sau:

Với:

- Sampling Time = thời gian tụ điện nạp điện (được cài đặt trong thanh ghi SMPRx).

- Channel Conversion Time = thời gian ADC thực hiện chuyển đổi (với SAR ADC, mất n xung clock để chuyển đổi n-bit).

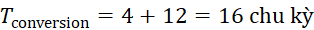

Ví dụ với STM32L (12-bit ADC, clock 16MHz):

🔹 Sampling Time = 4 chu kỳ

🔹 Channel Conversion Time = 12 chu kỳ

🔹 Tổng thời gian chuyển đổi:

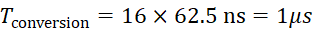

Với clock 16MHz (chu kỳ 62.5ns), ta có:

Vậy ADC có thể lấy mẫu với tốc độ 1 triệu mẫu/giây (1 MSPS).

Xem thêm: Giao thức truyền thông Local Interconnect Network (LIN)

Lỗi Lấy Mẫu (Sampling Error)

1. Cách ADC Chuyển Đổi Tín Hiệu Analog Sang Số

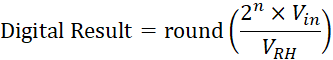

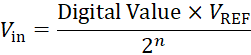

Khi một điện áp đầu vào Vin được đưa vào bộ ADC có độ phân giải n bit, giá trị số thu được (digital result) sẽ được tính theo công thức:

Trong đó:

- Vrh là điện áp tham chiếu cao (VREF+).

- Vrl là điện áp tham chiếu thấp (VREF-).

- Hàm round() dùng để làm tròn kết quả.

2. Hai Chế Độ Chuyển Đổi ADC

a. Chế độ single-end (Đơn cực)

- Vrl = 0, đầu ra ADC là số không dấu (unsigned).

- Công thức sẽ trở thành:

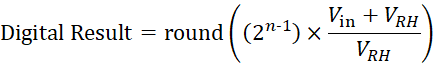

b. Chế độ dual-end: (Hai đầu vào – Hai cực)

- Vrl = -Vrh, đầu ra ADC là số có dấu (signed) dạng bù hai (two’s complement).

- Công thức:

3. Lỗi lấy mẫu ADC (ADC Sampling Error)

Lỗi xảy ra do hai yếu tố chính:

- Lỗ lượng tử hóa (Quantization Error):

- Lỗi lượng tử hóa là sai số giữa giá trị thực tế của tín hiệu đầu vào và giá trị số sau khi chuyển đổi. Do ADC có số bit hữu hạn, nó không thể biểu diễn mọi giá trị mà chỉ có thể đại diện cho một số mức điện áp rời rạc.

- Lỗi do tần số lấy mẫu:

- Nếu lấy mẫu quá chậm, tín hiệu bị méo.

- Tăng tần số lấy mẫu sẽ giúp giảm sai số.

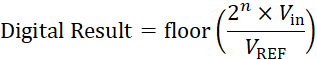

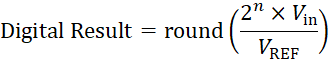

4. Phương pháp lượng tử hóa

Trong chế độ single-end với Vref = 5V, có hai phương pháp lượng tử hóa:

- Phương pháp floor(): Kết quả bị cắt bớt phần thập phân.

- Phương pháp round():: Làm tròn về giá trị gần nhất, giúp giảm lỗi trung bình xuống một nửa so với floor():

5. Tăng độ chính xác ADC

Để giảm lỗi chuyển đổi ADC, ta có thể:

- Tăng số bit ADC: Số bit càng cao thì sai số càng nhỏ.

- Tăng tần số lấy mẫu: Giúp tín hiệu được ghi nhận chính xác hơn.

Cuối cùng, ta có thể tính toán lại giá trị điện áp từ kết quả số bằng công thức:

Điều này giúp ta chuyển đổi ngược lại từ giá trị số về tín hiệu tương ứng.

Xem thêm: Timer là gì? Ứng dụng của timer trong Hệ thống nhúng

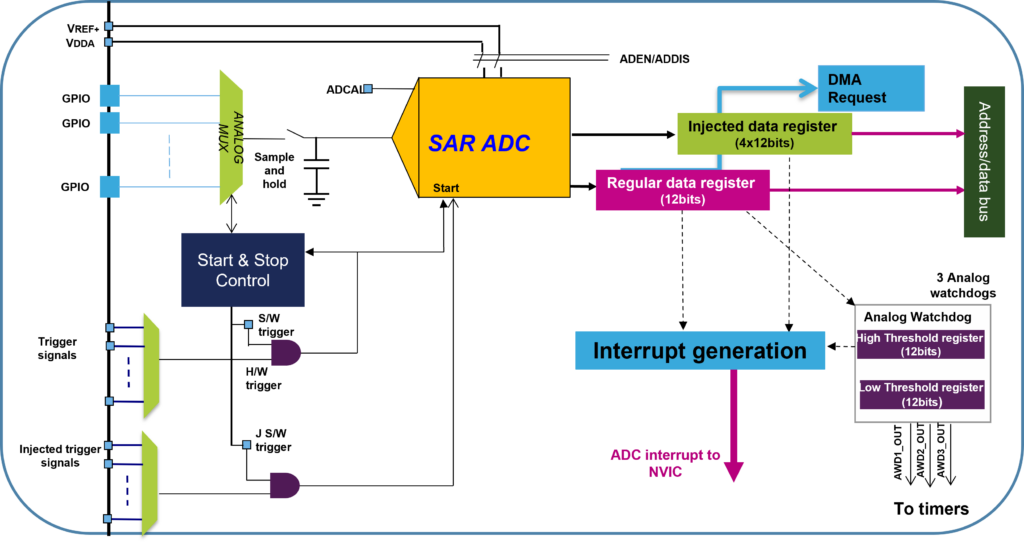

ADC Diagram

1. Độ phân giải (Resolution)

ADC có thể hoạt động ở các mức độ phân giải 12-bit, 10-bit, 8-bit hoặc 6-bit, tùy theo yêu cầu của ứng dụng.

Sử dụng oversampling, độ phân giải có thể nâng lên 16-bit, giúp đo lường chính xác hơn.

2. Dải điện áp đầu vào

Điện áp đầu vào của ADC nằm trong khoảng [Vref- , Vref+].

Vref- và Vref+ có thể là nguồn tham chiếu bên ngoài (nếu vi điều khiển hỗ trợ) hoặc nguồn tham chiếu nội bộ.

Một số vi điều khiển có một điện áp tham chiếu nội bộ (Vrefint) khoảng 3V ± 0.01V, được hiệu chuẩn và lưu trong bộ nhớ bảo vệ khi sản xuất.

3. Xung nhịp và tốc độ chuyển đổi

Các module ADC sử dụng chung một xung nhịp, có thể lấy từ ba nguồn khác nhau: PLLADC (PLL Output), SYSCLK (hệ thống clock), HCLK/Divider (bus clock chia tần số).

Xung nhịp ADC có thể độc lập với xung nhịp CPU.

Khi chạy ở 80 MHz, một ADC có thể đạt 5.33 triệu mẫu/giây với độ phân giải 12-bit.

Nếu giảm độ phân giải, tốc độ chuyển đổi có thể còn cao hơn.

4. Analog Watchdog (AWD)

Analog Watchdog (AWD) là bộ giám sát điện áp đầu vào của ADC.

Mỗi AWD có hai ngưỡng có thể lập trình: ngưỡng trên và ngưỡng dưới.

Nếu giá trị ADC nằm ngoài ngưỡng, có thể phát ngắt (interrupt) để xử lý bằng phần mềm hoặc kích hoạt các cơ chế bảo vệ hệ thống.

Ứng dụng của AWD:

🔹 Giám sát cảm biến nhiệt độ, điện áp, hoặc tín hiệu quan trọng.

🔹 Giúp hệ thống phản ứng nhanh khi giá trị đo vượt quá giới hạn mà không cần CPU kiểm tra liên tục → tiết kiệm tài nguyên xử lý.

Các chế độ chuyển đổi

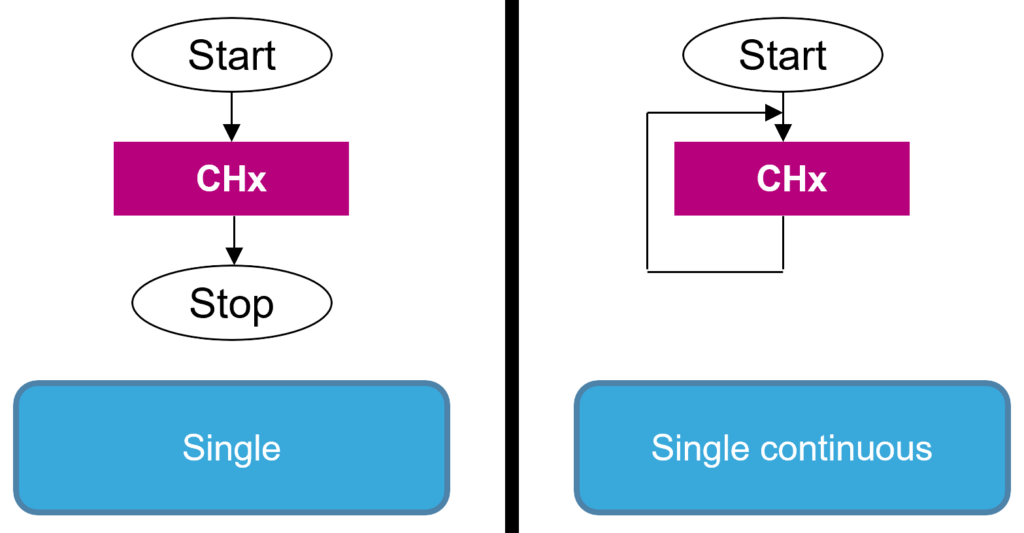

1. Sử dụng 1 kênh đầu vào

Khi ADC thực hiện chuyển đổi đơn, nó sẽ lấy mẫu tín hiệu đầu vào một lần, sau đó thực hiện chuyển đổi từ tín hiệu analog sang số và lưu kết quả vào thanh ghi dữ liệu ADC.

Nếu kênh nằm trong nhóm regular, kết quả sẽ được lưu vào thanh ghi dữ liệu ADC (ADC_DR). Khi quá trình chuyển đổi hoàn tất, cờ EOC (End of Conversion) sẽ được đặt, có thể kích hoạt ngắt nếu được cấu hình.

Nếu kênh nằm trong nhóm injected (nhóm này có độ ưu tiên cao hơn nhóm regular – Khi có yêu cầu chuyển đổi, ADC sẽ tạm dừng nhóm regular, thực hiện chuyển đổi nhóm injected trước rồi mới tiếp tục nhóm regular), kết quả sẽ được lưu vào thanh ghi dữ liệu ADC_JDR, và cờ JEOC (End of Injected Conversion) sẽ được đặt sau khi hoàn thành.

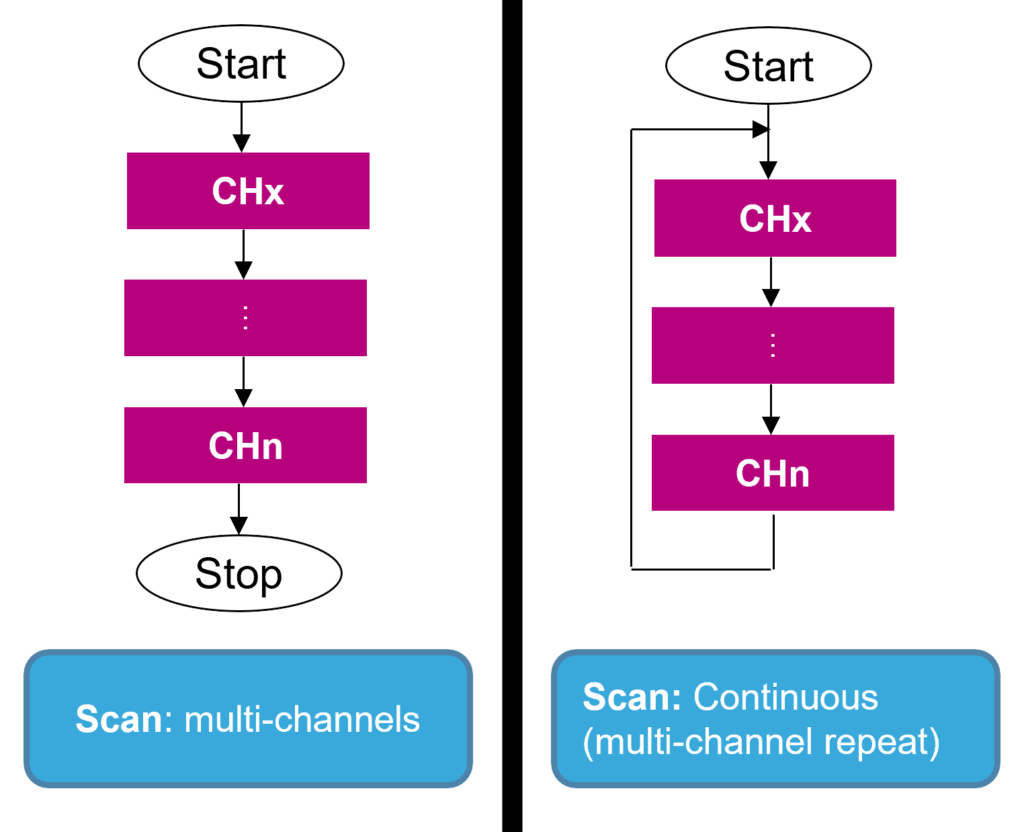

2. Sử dụng đa kênh đầu vào

ADC có thể thực hiện đo lường trên nhiều kênh đầu vào theo một danh sách được thiết lập sẵn. Quá trình này được gọi là chế độ quét (Scan Mode). Chế độ quét giúp ADC lần lượt chuyển đổi từng kênh trong danh sách, sau đó tiếp tục với kênh tiếp theo theo thứ tự đã định sẵn.

🔹 Nhóm regular chỉ có một vùng lưu trữ kết quả chung, vì vậy sau mỗi lần đo, phần mềm cần đọc dữ liệu trước khi giá trị mới ghi đè lên.

🔹 Nhóm injected có vùng lưu trữ riêng cho từng kênh, giúp tránh mất dữ liệu giữa các lần đo.

ADC có thể hoạt động theo hai cách:

🔹 Chuyển đổi một lần: Sau khi đo hết các kênh trong danh sách, ADC sẽ dừng lại.

🔹 Chuyển đổi liên tục: ADC tự động lặp lại quá trình đo mà không cần phần mềm kích hoạt lại.

Để tránh mất dữ liệu, kết quả đo cần được lưu trữ vào bộ nhớ đệm của người dùng. Điều này có thể thực hiện bằng ngắt ADC hoặc DMA để tự động sao chép dữ liệu, giúp giảm tải cho CPU.

Xem thêm: Ngắt là gì? Tầm quan trọng của ngắt trong hệ thống nhúng

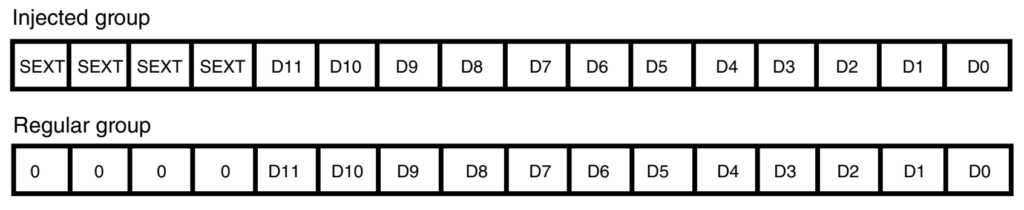

ADC Data Alignment

Khi ADC chuyển đổi tín hiệu, độ phân giải có thể được thiết lập thành 12, 10, 8 hoặc 6 bit. Tuy nhiên, kết quả đo được lưu trong các thanh ghi có độ rộng 16 bit, nên cần có cách căn chỉnh dữ liệu để đảm bảo giá trị được lưu đúng vị trí trong bộ nhớ.

1. Hai kiểu căn chỉnh dữ liệu

Căn phải (Right-aligned):

🔹 Kết quả đo được đặt về phía phải của thanh ghi, phần dư bên trái sẽ là các bit 0.

🔹 Phù hợp khi xử lý dữ liệu dạng số nguyên không dấu.

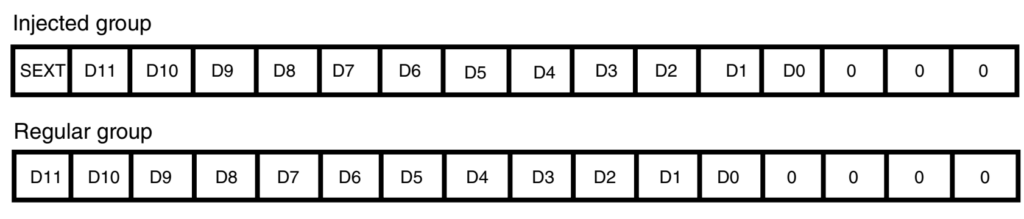

Căn trái (Left-aligned):

🔹 Dễ dàng xử lý khi cần mở rộng số liệu sang các định dạng có độ rộng lớn hơn.

🔹 Kết quả đo được đặt về phía trái của thanh ghi, phần dư bên phải sẽ là các bit 0.

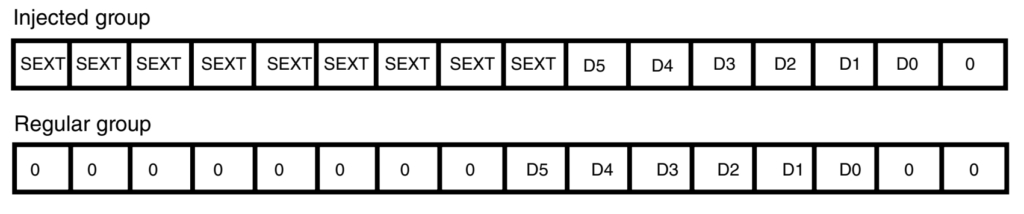

2. Xử lý khi có bù (Offset Correction)

Khi đọc dữ liệu ADC, đôi khi ta muốn trừ đi một giá trị cố định trước khi lưu kết quả. Điều này gọi là bù giá trị.

Khi sử dụng nhóm Injected, có thể thiết lập giá trị bù (offset) cho từng kênh.

Với nhóm Regular, ADC không trừ giá trị bù, nên kết quả luôn là số không âm (từ 0 đến giá trị tối đa).

Ví dụ: Nếu cảm biến nhiệt độ của bạn có độ lệch +10°C, bạn có thể đặt giá trị bù là 10 để ADC tự động trừ đi trước khi đưa ra kết quả.

Bình thường, ADC chỉ đo được giá trị dương (từ 0 đến giá trị tối đa). Nhưng nếu dùng bù giá trị, kết quả có thể trở thành số âm. Khi đó, ta cần lưu dữ liệu theo định dạng số có dấu để đảm bảo giá trị được hiểu đúng.

Trong hệ nhị phân, số có dấu được biểu diễn bằng bit dấu (bit bên trái nhất). Khi mở rộng độ rộng dữ liệu (ví dụ từ 8 bit lên 16 bit), ta lặp lại bit dấu lên các bit dư để giữ nguyên giá trị số.

Ví dụ:

🔹 Khi mở rộng lên 16 bit, ta lặp lại bit dấu (1): 11111111 11010110 (vẫn là -42).

🔹 Số nhị phân 8 bit: 11010110 (-42 trong hệ thập phân).

3. Trường hợp đặc biệt

ADC có thể xuất kết quả với độ phân giải 12, 10, 8 hoặc 6 bit. Nhưng vì bộ nhớ thường lưu dữ liệu theo từng khối cố định (thường là 8 bit = 1 byte hoặc 16 bit = 1 halfword), nên cần căn chỉnh dữ liệu để dễ dàng truy xuất.

a. Dữ liệu 12, 10, 8, 6 bit được căn chỉnh theo từng halfword khi căn phải:

Halfword = 16 bit, tức là mỗi ô nhớ sẽ chứa tối đa 16 bit. Do đó dữ liệu ADC (12, 10, 8, 6 bit) nhỏ hơn 16 bit, nên chúng sẽ được căn chỉnh vào halfword để tối ưu hiệu suất truy xuất.

b. Đối với dữ liệu 6 bit khi căn trái:

Khi căn trái, dữ liệu 12, 10, 8 bit được căn chỉnh theo từng halfword nhưng đối với dữ liệu 6 bit được căn chỉnh theo byte:

Vì 6 bit nhỏ hơn 8 bit (1 byte), nên nó sẽ được lưu theo định dạng byte. Phần còn thiếu sẽ được lấp đầy bằng các bit 0 để đảm bảo đúng kích thước bộ nhớ.

Tóm lại, ADC đóng vai trò quan trọng trong các hệ thống nhúng, giúp chuyển đổi tín hiệu tương tự thành dữ liệu số để vi điều khiển xử lý. Việc lựa chọn ADC phù hợp cần cân nhắc tốc độ lấy mẫu, độ phân giải và công suất tiêu thụ để đảm bảo hiệu suất hệ thống. Hiểu rõ về các kiến trúc ADC như SAR, Sigma-Delta hay Pipelined cùng cách tối ưu thời gian lấy mẫu và giảm lỗi chuyển đổi sẽ giúp tận dụng tối đa khả năng của ADC trong thiết kế mạch và ứng dụng thực tế.

Xem thêm: Tổng quan kiến trúc ARM Cortex-M3

Bút hút chân không

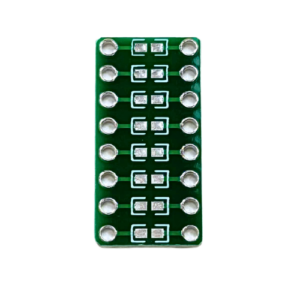

Bút hút chân không Breakout 0402 0603 0805

Breakout 0402 0603 0805 Antenna 9DBI 4G/3G/GSM/NB-IOT

Antenna 9DBI 4G/3G/GSM/NB-IOT