Tổng số phụ: 37.800 VNĐ (gồm VAT)

Quad Serial Peripheral Interface (Quad-SPI) là gì? Để lại bình luận

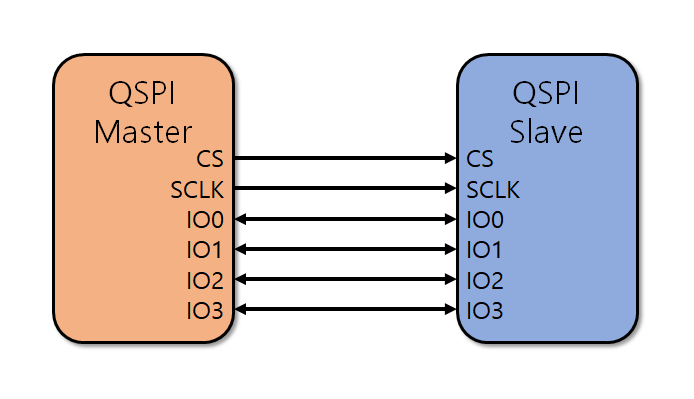

Quad-SPI (QSPI) là một giao tiếp nối tiếp giúp các vi điều khiển trao đổi dữ liệu với bộ nhớ ngoài qua bốn đường dữ liệu. Quad-SPI hỗ trợ cả chế độ SPI truyền thống (1 đường dữ liệu) và Dual-SPI (2 đường dữ liệu), nhưng khi ở chế độ Quad-SPI, nó sử dụng tối đa 6 đường: một đường chọn chip (CS), một đường xung nhịp (CLK) và bốn đường dữ liệu (D0-D3) để truyền và nhận dữ liệu nhanh hơn so với SPI thông thường.

So sánh Quad-SPI với SPI truyền thống và các giao thức song song khác

Quad-SPI có tốc độ truyền dữ liệu cao hơn nhiều so với SPI truyền thống vì sử dụng bốn đường dữ liệu thay vì một, giúp tăng thông lượng gần gấp bốn lần.

So với FMC và các giao tiếp song song khác, Quad-SPI cho phép kết nối bộ nhớ Flash ngoài với chi phí thấp hơn, tiết kiệm diện tích PCB, đơn giản hóa thiết kế và giảm số lượng GPIO cần sử dụng. Ở chế độ Quad-SPI, chỉ cần 6 GPIO (4 đường dữ liệu, 1 đường xung nhịp và 1 đường chọn chip), còn ở chế độ Dual-Flash Quad-SPI, số GPIO sử dụng là 10, với 8 đường dành cho dữ liệu.

Xem thêm: Tổng quan về giao thức SPI

Các chân kết nối của Quad-SPI

Giao tiếp Quad-SPI (QSPI) sử dụng các chân sau để kết nối với bộ nhớ Flash ngoài:

- CLK (Clock – Xung nhịp): Tín hiệu đồng hồ điều khiển tốc độ truyền dữ liệu giữa STM32 và bộ nhớ ngoài.

- CS (Chip Select – Chọn chip): Chân điều khiển để chọn bộ nhớ Flash cần giao tiếp, thường ở mức thấp khi hoạt động.

- DQ0 (IO0 – Data Line 0): Đường dữ liệu hai chiều, truyền hoặc nhận dữ liệu.

- DQ1 (IO1 – Data Line 1): Đường dữ liệu hai chiều, hỗ trợ chế độ Dual-SPI và Quad-SPI.

- DQ2 (IO2 – Data Line 2): Đường dữ liệu hai chiều, chỉ dùng trong chế độ Quad-SPI.

- DQ3 (IO3 – Data Line 3): Đường dữ liệu hai chiều, chỉ dùng trong chế độ Quad-SPI.

Ở chế độ Dual-Flash Quad-SPI, một số vi điều khiển như STM32 có thể giao tiếp với hai bộ nhớ Flash song song, mở rộng số đường dữ liệu:

- Thêm 4 chân dữ liệu (DQ4 – DQ7) để tăng tốc độ truyền tải dữ liệu.

- Tổng cộng cần 10 GPIO (bao gồm 8 đường dữ liệu, 1 xung nhịp, 1 chọn chip).

Cách kết nối này giúp tối ưu số chân sử dụng trên vi điều khiển mà vẫn đạt hiệu suất cao khi truy xuất bộ nhớ ngoài.

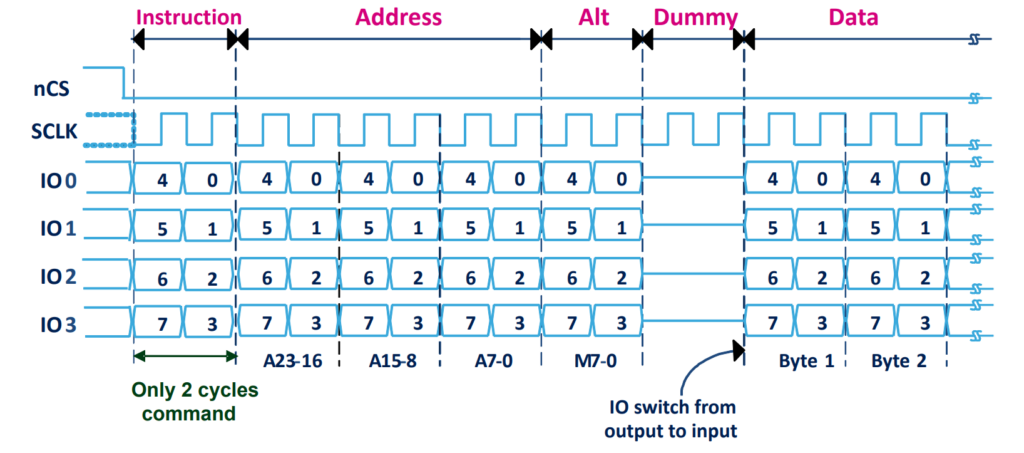

Frame format

Trong giao tiếp Quad-SPI, quá trình truyền dữ liệu được chia thành năm giai đoạn khác nhau, và mỗi giai đoạn có thể được tùy chỉnh về số lượng bit truyền và số đường dữ liệu sử dụng. Điều này giúp linh hoạt trong cách gửi lệnh và dữ liệu đến bộ nhớ Flash ngoài.

Tuy nhiên, việc cấu hình định dạng khung truyền (Frame format) chỉ áp dụng cho hai chế độ:

- Chế độ gián tiếp (Indirect mode) – Vi điều khiển gửi lệnh để đọc/ghi dữ liệu theo từng lần truy vấn.

- Chế độ ánh xạ bộ nhớ (Memory-mapped mode) – Bộ nhớ Flash ngoài hoạt động như RAM, có thể đọc dữ liệu trực tiếp mà không cần gửi lệnh mỗi lần.

Ngược lại, chế độ kiểm tra cờ trạng thái (Status-flag polling mode) chỉ dùng để kiểm tra trạng thái bộ nhớ Flash (ví dụ: đang bận hay đã sẵn sàng) và không thể cấu hình định dạng khung truyền trong chế độ này.

Ở chế độ Quad I/O SDR, dữ liệu được truyền theo từng bit trên bốn đường dữ liệu trong mỗi chu kỳ xung nhịp, giúp tăng tốc độ truyền dữ liệu so với SPI truyền thống chỉ dùng một đường dữ liệu.

Xem thêm: Tầm quan trọng của ngắt trong hệ thống nhúng

a. Giai đoạn Instruction

Giai đoạn Instruction (Lệnh) là bước đầu tiên trong quá trình giao tiếp giữa vi điều khiển và bộ nhớ Flash ngoài qua Quad-SPI. Trong giai đoạn này, một lệnh (8-bit) được gửi đến bộ nhớ để xác định loại thao tác cần thực hiện, chẳng hạn như đọc, ghi hoặc xóa dữ liệu.

Các Đặc Điểm Chính:

- Lệnh được cấu hình thông qua thanh ghi của Quad-SPI.

- Có thể gửi lệnh qua 1, 2 hoặc 4 đường dữ liệu, tùy thuộc vào cấu hình phần cứng và phần mềm.

- Trong một số trường hợp, nếu chỉ cần gửi địa chỉ mà không cần lệnh, giai đoạn này có thể bị bỏ qua.

- Giai đoạn Instruction luôn chạy ở chế độ SDR (Single Data Rate), ngay cả khi hệ thống đang ở chế độ DDR (Double Data Rate).

Các Chế Độ Gửi Lệnh:

Bỏ qua giai đoạn Instruction (IMODE = 00): Khi không cần gửi lệnh.

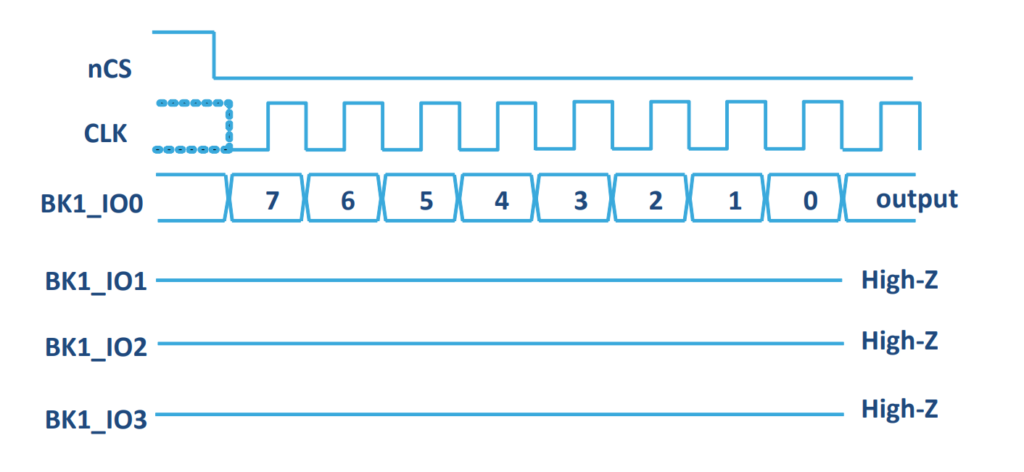

Gửi lệnh trên 1 đường dữ liệu (Single-SPI) (IMODE = 01): Lệnh được gửi tuần tự qua một chân dữ liệu:

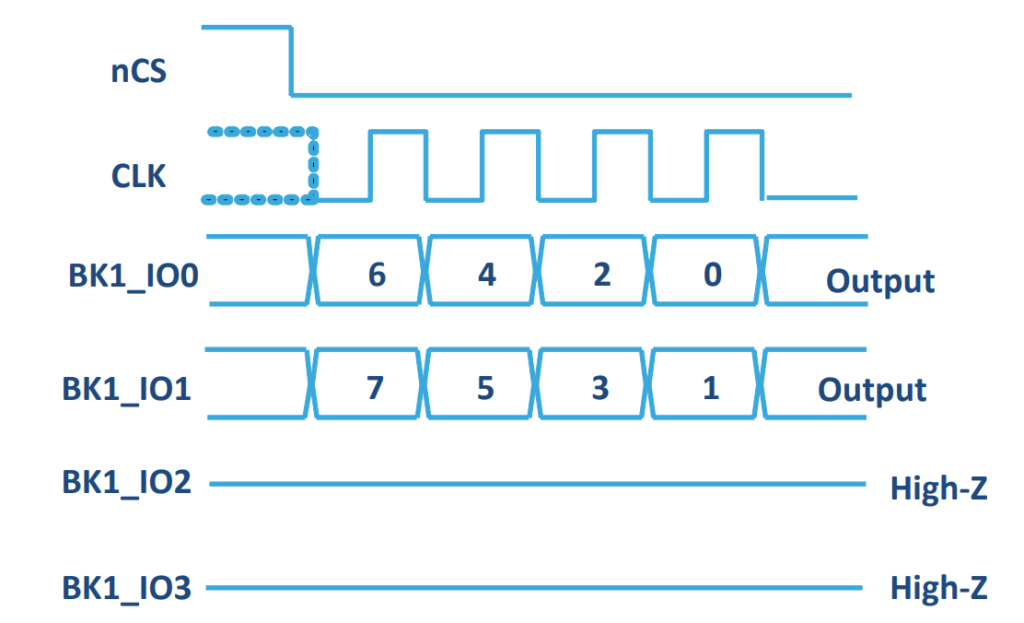

Gửi lệnh trên 2 đường dữ liệu (Dual-SPI) (IMODE = 10): Lệnh được chia nhỏ và gửi đồng thời trên hai chân dữ liệu:

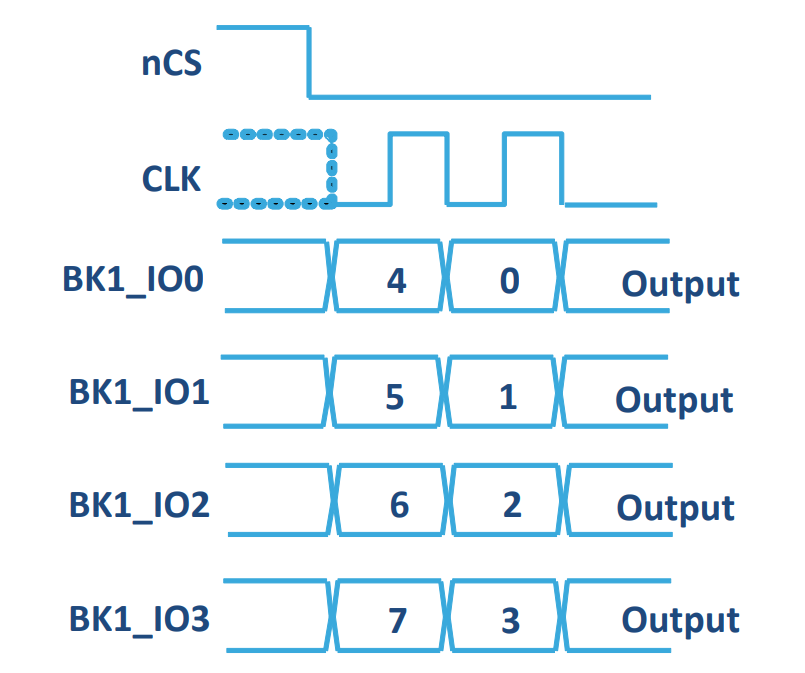

Gửi lệnh trên 4 đường dữ liệu (Quad-SPI) (IMODE = 11): Lệnh được chia thành bốn phần và gửi cùng lúc trên bốn chân dữ liệu, giúp tăng tốc độ:

b. Giai đoạn Address

Giai đoạn địa chỉ là bước gửi thông tin về vị trí trong bộ nhớ Flash để thực hiện thao tác đọc, ghi hoặc xóa dữ liệu.

Số byte địa chỉ có thể gửi (1-4 bytes):

- Độ dài địa chỉ được cấu hình trong thanh ghi tuỳ theo vi điều khiển.

- Bộ nhớ Flash có thể yêu cầu 1, 2, 3 hoặc 4 byte địa chỉ tùy vào dung lượng bộ nhớ.

Ví dụ:

- Flash 16MB (128 Mbit) → cần 3 byte địa chỉ (24-bit).

- Flash 256MB (2 Gbit) → cần 4 byte địa chỉ (32-bit).

Cách gửi địa chỉ trong các chế độ khác nhau:

- Chế độ Indirect & Automatic-Polling: Địa chỉ cần gửi được ghi vào thanh ghi phù hợp.

- Chế độ Memory-Mapped: Địa chỉ không cần ghi vào thanh ghi mà được gửi trực tiếp từ CPU hoặc DMA thông qua bus AHB.

Cách gửi địa chỉ qua các đường tín hiệu (Lines):

- Single-SPI Mode: Địa chỉ gửi từng bit một (qua IO0/SO).

- Dual-SPI Mode: Địa chỉ gửi 2 bit mỗi chu kỳ (qua IO0, IO1).

- Quad-SPI Mode: Địa chỉ gửi 4 bit mỗi chu kỳ (qua IO0, IO1, IO2, IO3).

Có thể bỏ qua giai đoạn địa chỉ khi không cần gửi địa chỉ, ví dụ lệnh xóa toàn bộ Flash (Mass Erase).

c. Giai đoạn Alternate-Byte

Giai đoạn alternate-byte là một bước tùy chọn trong giao tiếp Quad-SPI, cung cấp tính linh hoạt bổ sung. Giai đoạn này thường được sử dụng để kiểm soát chế độ hoạt động của bộ nhớ Flash.

Mục đích của Alternate-Byte Phase:

- Một số bộ nhớ Flash yêu cầu gửi liên tục một byte bổ sung để duy trì chế độ hoạt động, ví dụ như chế độ Execute-In-Place (XIP).

- Giai đoạn này được hỗ trợ bởi một số nhà sản xuất bộ nhớ như Spansion, Micron, Macronix.

Ví dụ:

- Một số dòng Flash cần gửi liên tục giá trị 0xA5 để duy trì chế độ XIP khi đang thực thi mã trực tiếp từ Flash.

- Nếu hệ thống không cần chức năng này, giai đoạn alternate-byte có thể được bỏ qua.

Cấu hình Alternate-Byte:

Có thể gửi 1, 2, 3 hoặc 4 byte tùy theo nhu cầu. Dữ liệu gửi trong giai đoạn này có thể được thiết lập trước để phù hợp với bộ nhớ Flash đang sử dụng.

Cách gửi Alternate-Byte qua các đường truyền:

- 1 đường (Single-SPI) → Gửi qua một đường tín hiệu.

- 2 đường (Dual-SPI) → Gửi song song 2 bit mỗi chu kỳ.

- 4 đường (Quad-SPI) → Gửi song song 4 bit mỗi chu kỳ.

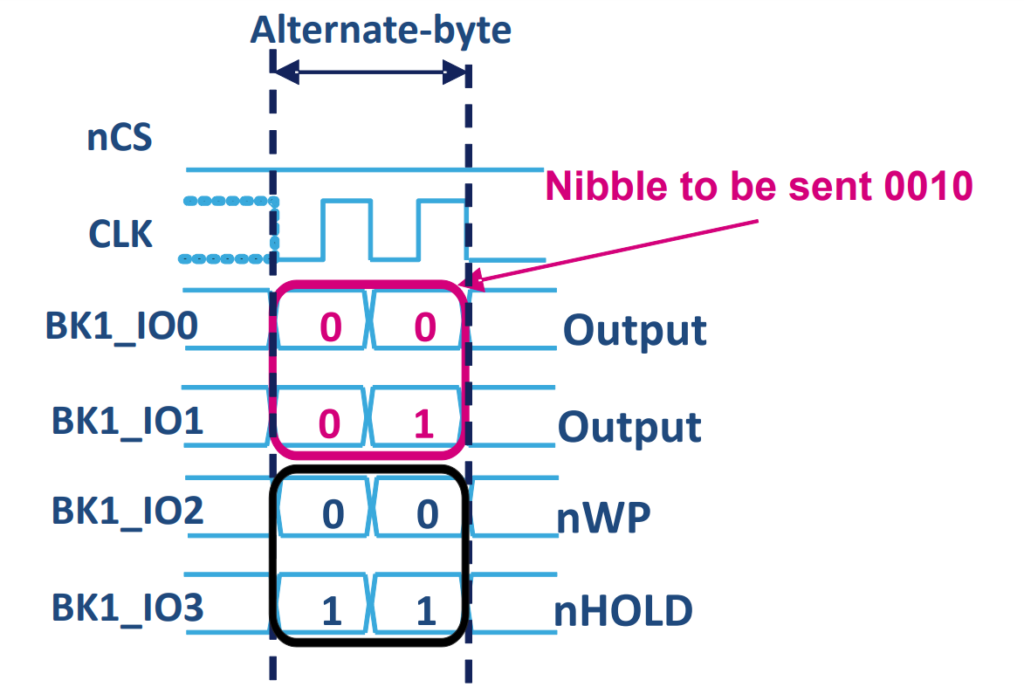

Giai đoạn Alternate-Byte: Gửi Nibble trong Dual-SPI Mode:

Trước tiên, nibble là gì?

- Một byte có 8 bit, có thể chia thành hai phần:

- Nibble cao (High Nibble): 4 bit đầu tiên.

- Nibble thấp (Low Nibble): 4 bit còn lại.

- Ví dụ: Byte 0x9A có thể chia thành:

- High Nibble: 9 (1001)

- Low Nibble: A (1010)

Vì sao chỉ gửi một nibble thay vì cả byte?

- Trong Dual-SPI mode, dữ liệu thường được gửi qua 2 đường truyền (IO0 và IO1) mỗi chu kỳ.

- Thông thường, để gửi 1 byte (8 bit), ta cần 4 chu kỳ clock vì mỗi chu kỳ chỉ truyền 2 bit.

- Nhưng nếu chỉ cần gửi 1 nibble (4 bit), ta chỉ cần 2 chu kỳ clock, giúp giảm độ trễ và tăng tốc độ truyền dữ liệu.

Quad I/O mode chỉ kích hoạt trong giai đoạn này

- Trong giai đoạn này, ta không sử dụng IO2 và IO3 để gửi dữ liệu, nhưng cần duy trì mức tín hiệu:

- IO2 giữ mức thấp (0).

- IO3 giữ mức cao (1).

- Việc giữ ổn định IO2 và IO3 giúp đảm bảo không có tín hiệu nhiễu, đặc biệt là khi bộ nhớ Flash yêu cầu trạng thái ổn định trong quá trình truyền dữ liệu.

Xem thêm: Hệ thống nhúng là gì? Cái nhìn tổng quan về hệ thống nhúng

d. Giai đoạn Dummy-Cycle

Vì sao cần giai đoạn Dummy-Cycle?

- Khi vi điều khiển giao tiếp với bộ nhớ Flash ở tốc độ cao, có một khoảng thời gian cần thiết để chuyển trạng thái từ gửi lệnh (output) sang nhận dữ liệu (input).

- Nếu không có giai đoạn này, bộ nhớ Flash có thể chưa kịp chuẩn bị dữ liệu, dẫn đến lỗi đọc sai thông tin.

Ví dụ:

- Khi sử dụng Fast Read (0x0B) thay vì Read thông thường (0x03), Flash cần thêm dummy cycles để chuẩn bị dữ liệu.

- Nếu không có dummy cycles, dữ liệu nhận được có thể bị lệch hoặc sai.

Cấu hình số lượng Dummy Cycles

- Số chu kỳ dummy có thể lên đến 31 chu kỳ clock và được thiết lập trước khi gửi lệnh.

- Một dummy cycle luôn tương ứng với 1 chu kỳ clock, dù là SDR (Single Data Rate) hay DDR (Double Data Rate).

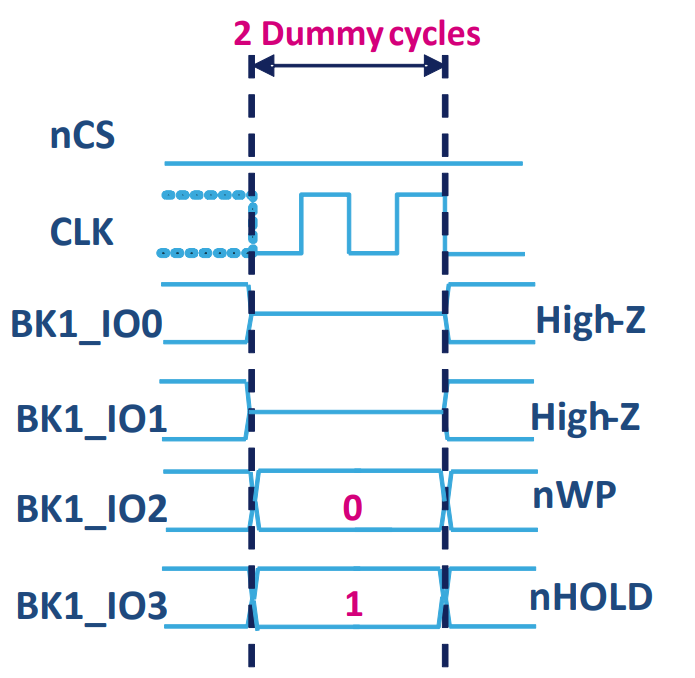

Dummy-Cycle và IO2, IO3

- Trong chế độ Quad-SPI hoặc Dual-SPI, IO2 và IO3 có vai trò đặc biệt trong giai đoạn này:

- IO2 được đặt ở mức thấp (0) → Vô hiệu hóa chức năng Write-Protect (WP).

- IO3 được đặt ở mức cao (1) → Vô hiệu hóa chức năng Hold (HOLD).

- Đây là cơ chế tự động của phần cứng, không cần lập trình thủ công.

Minh họa hoạt động Dummy-Cycle

Trong giai đoạn Dummy-Cycle:

- Dữ liệu trên IO0 và IO1 ở trạng thái High-Z (không truyền dữ liệu).

- IO2 và IO3 giữ mức 0 và 1 để đảm bảo không bị kích hoạt chức năng không mong muốn.

e. Giai đoạn data

Giai đoạn Data là bước truyền hoặc nhận dữ liệu giữa vi điều khiển và bộ nhớ Flash Quad-SPI.

Chức năng của giai đoạn dữ liệu

- Gửi dữ liệu đến bộ nhớ Flash (Write).

- Nhận dữ liệu từ bộ nhớ Flash (Read).

- Có thể gửi hoặc nhận một số lượng byte bất kỳ.

Lưu ý:

- Nếu thực hiện xóa bộ nhớ (Erase), không có dữ liệu cần gửi hoặc nhận, do đó có thể bỏ qua giai đoạn này.

Cách xử lý dữ liệu trong các chế độ khác nhau

| Chế độ | Cách truyền dữ liệu |

| Indirect Mode | Vi điều khiển ghi dữ liệu vào hoặc đọc dữ liệu từ bộ nhớ thông qua thanh ghi dữ liệu. |

| Automatic-Polling Mode | Hệ thống tự động gửi dữ liệu để kiểm tra trạng thái của bộ nhớ Flash. |

| Memory-Mapped Mode | Vi điều khiển có thể đọc dữ liệu trực tiếp như một bộ nhớ trong, nhưng không thể ghi. |

Số lượng byte truyền tải

- Số lượng byte cần gửi hoặc nhận có thể được cấu hình trước.

- Nếu thiết lập giá trị tối đa (0xFFFFFFFF), hệ thống sẽ đọc hoặc ghi cho đến khi đạt đến địa chỉ cuối cùng của bộ nhớ Flash.

Trường hợp đặc biệt:

- Nếu thiết lập chế độ đọc vô hạn (FSIZE = 0x1F), hệ thống sẽ tiếp tục đọc mãi mãi cho đến khi bị dừng thủ công.

Cách truyền dữ liệu qua các đường tín hiệu

- 1 đường (Single-SPI) → Gửi dữ liệu qua 1 line (IO0).

- 2 đường (Dual-SPI) → Gửi dữ liệu song song qua 2 lines (IO0, IO1).

- 4 đường (Quad-SPI) → Gửi dữ liệu song song qua 4 lines (IO0, IO1, IO2, IO3).

Xem thêm: Tổng quan về kiến trúc ARM-Cortex M3

Các chế độ giao tiếp tín hiệu trong Quad-SPI

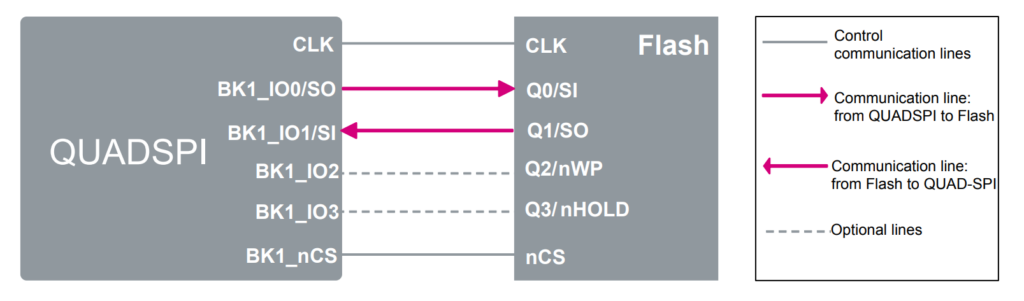

1. Single SPI Mode

- Dữ liệu được gửi/nhận từng bit một (1 bit mỗi chu kỳ clock).

- IO0 (SO) → Dữ liệu đầu ra (output).

- IO1 (SI) → Dữ liệu đầu vào (input, ở trạng thái High-Z khi không sử dụng).

- IO2 = 0, IO3 = 1 để vô hiệu hóa chức năng bảo vệ ghi (Write-Protect) và giữ dữ liệu (Hold).

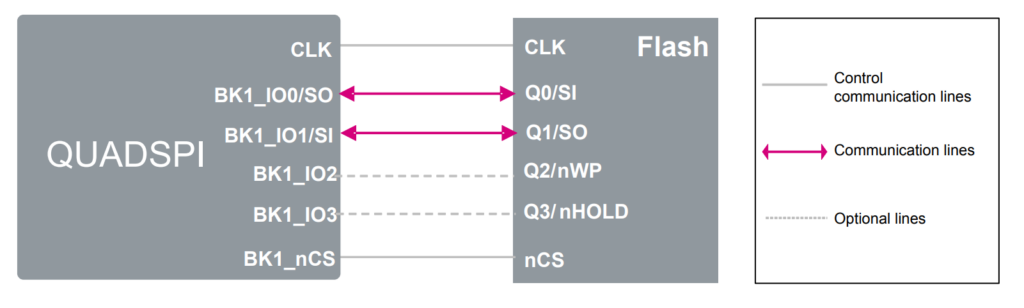

2. Dual SPI Mode

- Dữ liệu được gửi/nhận song song trên IO0 và IO1 (2 bit mỗi chu kỳ clock).

- IO0, IO1 → Có thể là đầu vào hoặc đầu ra, tùy thuộc vào giai đoạn truyền dữ liệu.

- IO2 = 0, IO3 = 1 để tránh kích hoạt chức năng không mong muốn.

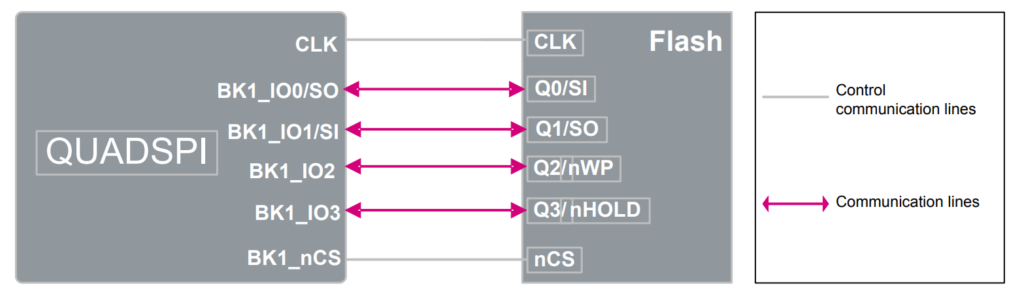

3. Quad SPI Mode

- Dữ liệu được gửi/nhận qua cả 4 đường IO0, IO1, IO2, IO3 (4 bit mỗi chu kỳ clock).

- Tất cả các IO đều có thể là đầu vào (input) hoặc đầu ra (output), tùy vào chế độ đọc/ghi.

- Chế độ nhanh nhất trong ba chế độ SPI.

4. SDR vs. DDR Mode

SDR (Single Data Rate – Truyền dữ liệu đơn cạnh)

- Mặc định, dữ liệu chỉ thay đổi trên cạnh xuống của xung clock (CLK).

- Khi nhận dữ liệu, hệ thống lấy mẫu trên cạnh lên của CLK.

- Tốc độ truyền: Chậm hơn DDR.

DDR (Double Data Rate – Truyền dữ liệu hai cạnh)

- Dữ liệu được gửi trên cả cạnh lên và cạnh xuống của CLK.

- Khi nhận dữ liệu, hệ thống lấy mẫu dữ liệu trên cả hai cạnh của CLK.

- Tốc độ truyền: Nhanh hơn SDR gấp đôi.

- Lưu ý: Lệnh (Instruction Phase) vẫn được gửi theo chế độ SDR.

Xem thêm: Xung clock – nhịp tim của hệ thống nhúng

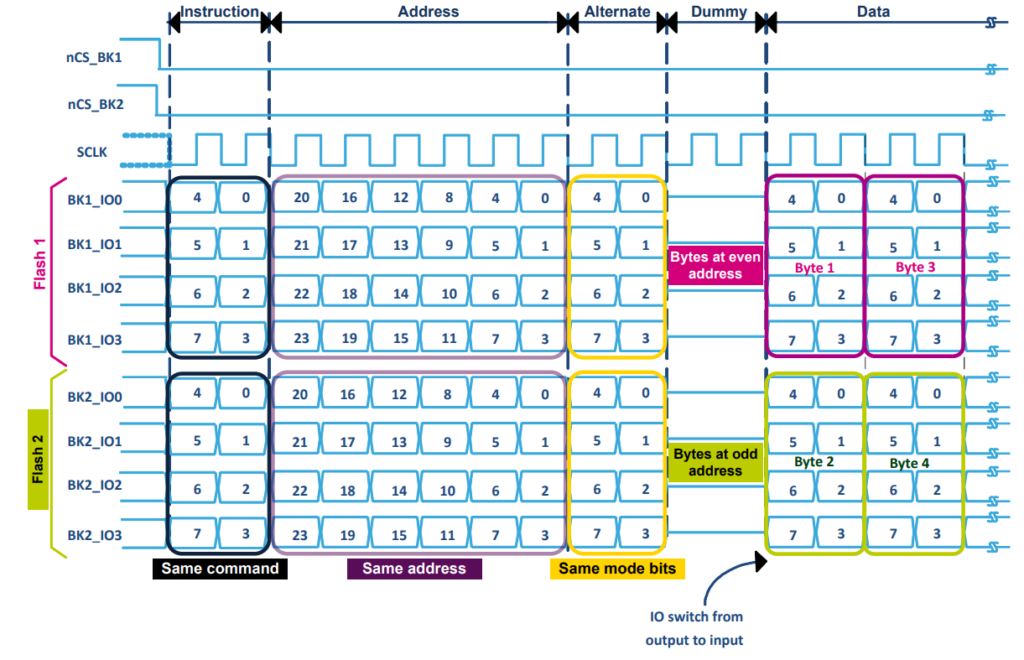

5. Dual-Flash Mode

Chế độ Dual-Flash cho phép vi điều khiển giao tiếp đồng thời với hai bộ nhớ Flash Quad-SPI. Điều này giúp tăng gấp đôi tốc độ truyền dữ liệu (throughput) và dung lượng bộ nhớ, trong khi chỉ sử dụng 10 chân GPIO.

a. Dual-Flash hoạt động như thế nào?

- Hai bộ nhớ Flash hoạt động song song, cùng nhận chung lệnh (instruction) và chung địa chỉ (address).

- Dữ liệu được chia đều giữa hai bộ nhớ:

- Byte tại địa chỉ chẵn → Lưu trong Flash 1.

- Byte tại địa chỉ lẻ → Lưu trong Flash 2.

- Khi đọc dữ liệu, vi điều khiển có thể đọc hai byte cùng lúc, giúp tăng gấp đôi tốc độ đọc/ghi.

Ví dụ:

- Đọc địa chỉ 0x90000000 – 0x90000003 trong chế độ Memory-Mapped:

- Gửi địa chỉ 0x00000000 đến cả Flash 1 và Flash 2.

- Flash 1 trả về Byte 1 (địa chỉ chẵn 0x90000000), Flash 2 trả về Byte 2 (địa chỉ lẻ 0x90000001).

- Tiếp tục gửi địa chỉ 0x00000001, Flash 1 trả về Byte 3 (0x90000002), Flash 2 trả về Byte 4 (0x90000003).

Kết quả:

- Vi điều khiển nhận được 2 byte mỗi chu kỳ, thay vì 1 byte như trong chế độ Single-Flash.

b. Cấu hình phần cứng của Dual-Flash

- Chỉ cần 1 chân nCS (Chip Select) để điều khiển cả hai bộ nhớ Flash.

- Cả hai bộ nhớ dùng chung CLK (Clock).

- 8 đường dữ liệu (IO0 – IO3 cho mỗi Flash), giúp truyền 8 bit song song trong SDR hoặc 16 bit trong DDR.

Xem thêm: Giao thức I3C là gì?

Ba chế độ hoạt động của Quad-SPI (QSPI)

1. Indirect Mode

Indirect Mode là một trong ba chế độ hoạt động của Quad-SPI (QSPI), cho phép MCU giao tiếp với bộ nhớ Flash ngoài theo kiểu đọc/ghi qua thanh ghi (register-based), thay vì ánh xạ trực tiếp vào không gian địa chỉ.

a. Khi nào sử dụng Indirect Mode?

- Đọc, ghi hoặc xóa dữ liệu

- Nếu cần ghi dữ liệu lên bộ nhớ Flash hoặc thực hiện lệnh xóa (erase), Indirect Mode bắt buộc phải được sử dụng.

- Không cần truy cập tự động từ AHB (Memory-Mapped không phù hợp)

- Nếu MCU không cần đọc bộ nhớ Flash như RAM (truy xuất trực tiếp qua AHB bus), thì Indirect Mode là một lựa chọn phù hợp.

- Sử dụng CPU hoặc DMA để trao đổi dữ liệu

- Dữ liệu được truyền tải thông qua các thanh ghi của QUADSPI bằng cách sử dụng CPU hoặc DMA (nếu muốn tối ưu hiệu suất).

- Cấu hình ban đầu cho bộ nhớ Flash

- Khi cần thiết lập bộ nhớ Flash ngoài (chẳng hạn như chế độ tốc độ cao, chế độ địa chỉ 4 byte…), MCU sẽ sử dụng Indirect Mode để gửi lệnh cấu hình.

b. Cách thức hoạt động của Indirect Mode

- Tất cả các thao tác đọc/ghi được thực hiện qua thanh ghi QUADSPI, không phải qua không gian địa chỉ.

- Bộ FIFO được sử dụng để lưu trữ dữ liệu tạm thời, giúp truyền dữ liệu nhanh hơn.

- MCU có thể sử dụng polling hoặc interrupt để kiểm tra trạng thái của bộ nhớ Flash.

c. Lưu ý quan trọng:

- Khi ghi hoặc xóa Flash, MCU phải kiểm tra trạng thái của Flash bằng Auto-Polling Mode để biết khi nào quá trình hoàn thành.

- Không thể thực hiện các thao tác ghi trực tiếp trong Memory-Mapped Mode, nên Indirect Mode phải được dùng.

2. Status-Flag Polling Mode

Chế độ Status-Flag Polling Mode được sử dụng để tự động kiểm tra trạng thái của bộ nhớ Flash thông qua thanh ghi trạng thái (status register).

a. Khi nào cần sử dụng chế độ này?

- Kiểm tra trạng thái của bộ nhớ Flash

- Ví dụ: Đọc thanh ghi trạng thái để biết bộ nhớ có đang bận không.

- Tự động kiểm tra khi nào một thao tác kết thúc

- Khi thực hiện ghi hoặc xóa Flash, bộ nhớ sẽ mất một khoảng thời gian để hoàn thành.

- Thay vì CPU phải kiểm tra liên tục, QSPI có thể tự động kiểm tra và thông báo khi quá trình kết thúc.

- Giảm tải cho CPU

- MCU không cần liên tục gửi lệnh đọc trạng thái → giúp CPU tiết kiệm tài nguyên.

- Đọc thanh ghi trạng thái theo chu kỳ định sẵn

- QSPI có thể được cấu hình để đọc một thanh ghi nhất định theo chu kỳ nhằm theo dõi các bit trạng thái.

b. Cách hoạt động của chế độ này

- QSPI sẽ tự động gửi lệnh đọc thanh ghi trạng thái của bộ nhớ Flash.

- Dữ liệu đọc được sẽ được so sánh với giá trị mong muốn thông qua match register.

- Khi có sự kiện phù hợp, một ngắt (interrupt) có thể được tạo ra để thông báo cho MCU.

Chế độ so sánh bit:

- AND mode: Chỉ khi tất cả các bit mong muốn khớp, một ngắt sẽ được tạo ra.

- OR mode: Chỉ cần một bit khớp, ngắt sẽ được tạo ra.

d. Lợi ích của Status-Flag Polling Mode

Tự động kiểm tra quá trình ghi/xóa mà không cần CPU giám sát thủ công.

Tiết kiệm tài nguyên CPU, giúp MCU xử lý các tác vụ khác trong khi chờ bộ nhớ hoàn thành thao tác.

Hỗ trợ tạo ngắt, giúp xử lý sự kiện nhanh chóng khi thao tác hoàn tất.

Xem thêm: Tổng quan về giao thức UART

3. Memory-Mapped Mode

Chế độ Memory-Mapped Mode cho phép bộ nhớ ngoài Quad-SPI hoạt động giống như bộ nhớ trong của vi điều khiển. Điều này giúp các bộ điều khiển bus AHB (bao gồm CPU, DMA, LTDC, v.v.) có thể truy cập bộ nhớ này trực tiếp mà không cần sự can thiệp của phần mềm.

a. Ứng dụng chính của Memory-Mapped Mode:

- Đọc dữ liệu từ bộ nhớ Flash ngoài một cách trực tiếp.

- Cho phép CPU thực thi mã lệnh từ bộ nhớ ngoài (XIP – Execute In Place).

- Giúp các AHB master như DMA, LTDC đọc dữ liệu mà không cần CPU can thiệp.

b. Cách hoạt động của Memory-Mapped Mode

- Khi được cấu hình ở chế độ Memory-Mapped Mode, bộ nhớ Flash ngoài sẽ được ánh xạ (mapped) vào không gian bộ nhớ hệ thống từ địa chỉ 0x9000 0000 đến 0x9FFF FFFF.

- Tất cả quá trình truyền nhận dữ liệu như gửi opcode, địa chỉ đều do phần cứng QUADSPI đảm nhận.

- Cơ chế prefetch buffer (bộ đệm nạp trước) giúp tối ưu hiệu suất đọc và thực thi mã từ bộ nhớ ngoài.

Lưu ý:

- Khi sử dụng Memory-Mapped Mode, không thể đọc trực tiếp thanh ghi dữ liệu QUADSPI_DR vì nó luôn trả về

0. - Chỉ hỗ trợ truy cập đọc (không hỗ trợ ghi trực tiếp).

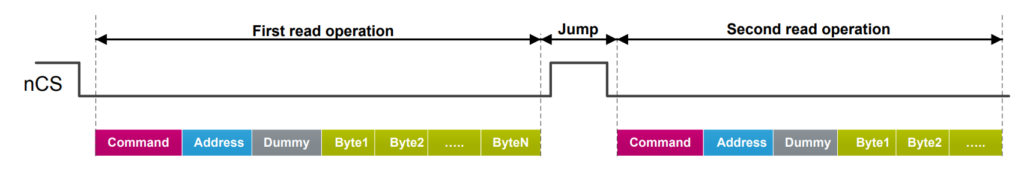

c. Execute in Place (XIP) – Thực thi mã trực tiếp từ bộ nhớ ngoài

- XIP (Execute In Place) cho phép CPU chạy mã trực tiếp từ bộ nhớ Quad-SPI mà không cần sao chép vào RAM. Cơ chế prefetch buffer giúp tối ưu tốc độ truy xuất bằng cách tải trước dữ liệu từ địa chỉ tiếp theo, đảm bảo truy cập nhanh hơn nếu CPU đọc tuần tự (Địa chỉ liên tục (Ví dụ: 0x01, 0x02, 0x03). Điều này giúp giảm độ trễ và cải thiện hiệu suất khi thực thi mã từ bộ nhớ ngoại.

- Nhưng khi có một jump (nhảy địa chỉ (Địa chỉ không liên tục (Ví dụ: 0x01, 0x05, 0x08))), prefetch buffer sẽ mất hiệu lực và phải khởi động lại quá trình đọc (thể hiện qua việc nCS được nhả ra và kích hoạt lại). Điều này dẫn đến việc cần gửi lại lệnh đọc và tốn thêm thời gian, làm giảm hiệu suất so với truy cập tuần tự.

d. Booting từ Quad-SPI Flash

Vi điều khiển sẽ khởi động từ bộ nhớ Flash nội trước, rồi cấu hình lại QUADSPI ở chế độ Memory-mapped. Sau khi cấu hình xong, chương trình có thể chạy trực tiếp từ Quad-SPI Flash như một bộ nhớ nội.

Quad-SPI mang lại tốc độ truyền dữ liệu cao hơn SPI truyền thống nhờ sử dụng nhiều đường dữ liệu, giúp cải thiện hiệu suất khi kết nối với bộ nhớ ngoài. So với các giao thức song song khác, nó giúp tiết kiệm số chân GPIO, đơn giản hóa thiết kế mạch và giảm chi phí phần cứng. Với khả năng hoạt động linh hoạt ở các chế độ như Indirect, Memory-Mapped hay Dual-Flash, giao tiếp này phù hợp để kết nối bộ nhớ ngoài trong các ứng dụng nhúng yêu cầu hiệu suất cao.

Xem thêm: Tất tần tật về giao thức I2C

Đế kẹp mạch DKM01

Đế kẹp mạch DKM01